A Peer Revieved Open Access International Journal

www.ijiemr.org

**COPY RIGHT**

2022 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 5th Mar 2022. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-11&issue=ISSUE-02

### DOI: 10.48047/IJIEMR/V11/I03/02

Title Enhanced Reverse Carry Propagate Adder For High Speed And Energy Efficient DSP Applications

Volume 11, Issue 03, Pages: 7-14 Paper Authors T Sai Karthik, M Sunder Rao

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

A Peer Reviewed Open Access International Journal

www.ijiemr.org

### Enhanced Reverse Carry Propagate Adder For High Speed And Energy Efficient DSP Applications

<sup>[1]</sup>T Sai Karthik, <sup>[2]</sup>M Sunder Rao

<sup>[1]</sup> PG Scholar, <sup>[2]</sup> Assistant Professor <sup>[1]</sup> t.saikarthik2k14@gmailcom, <sup>[2]</sup> malladi.sunderrao@gmail.com

**Abstract**— Digital signal processing (DSP) hardware acceleration has recently been shown to be a very promising implementation strategy. In this abstract, we provide an unique accelerator architecture based on flexible computational units that aids in the execution of a large number of operation templates accessible in DSP kernels rather than a monolithic application-specific integrated circuit design approach. Many digital signal processing applications depend on adders, including This study demonstrates a well-organized reverse carry propagate adder (RCPA). Due to the unique RCPA structure, a Carry signal is better suited for manufacturing since it propagates from the most significant bit (MSB) to the least significant bit (LSB) backwards. With delay variance, the stability of this propagation method is improved significantly. The n-bit adder architecture is similarly based on a hybrid structure in which the first half of the adder is added using a high-speed high-accuracy adder, such as Brent–Kung. We may boost the speed of the adder by employing the Brent–Kung adder, and at least half of the adder design is accomplished by using the Reverse Carry Propagate Adder (RCPA). Xilinx ISE 14.7 software and Verilog HDL coding are used to examine the structure of hybrid adders and compare it to that of standard approximation adders.

**Index Terms**— Approximate adder, Parallel Self Timed adder (PASTA), Digital signal processing (DSP), Reverse carry propagate adder (RCPA),

#### **INTRODUCTION**

Adder blocks, which are critical components of DSP systems' arithmetic units, use a lot of power and tend to generate hotspots in the die. These serve as the driving forces behind the approximation computing method used to create this kind of component. At the very least, general-purpose processors and DSP instruction sets incorporate some kind of addition. There are several operations that incorporate addition and whose underlying hardware is similar or identical to addition

subtraction hardware, such as and multiplication. If an adder is in the critical path, then the design's performance is generally limited by the performance of its numerous adders or adders. A chip's remaining properties, such as power or area, are more likely to be influenced by the hardware used for addition. There are a slew of additional considerations that come into play when making the decision about which adder to utilise in an application. As signal and computer processing applications grow,

A Peer Reviewed Open Access International Journal

#### www.ijiemr.org

the need for high-speed processing grows as well. Many image processing and real-time signal applications rely on faster arithmetic operations to meet their performance goals.

As a result of its growing popularity, digital signal processing (DSP) has been included into a large number of commercial processors. When compared to generalpurpose processors, DSPs have a wide range of architectures and features. The gain performance of these features determines the overall processor performance. Experiments on approximation adders have been done before.

Concentrate on reducing errors through reducing the frequency of errors and increasing the weight of errors. Designing digital processing units, particularly portable systems, has as its primary objectives reducing power consumption and increasing speed. For certain processing units, an increase in speed is often accompanied by an increase in power consumption. Increasing throughput at the expense of precision may also be an option for increasing both speed and power.

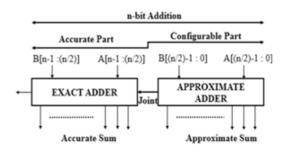

Approximate computing is the method used in this project. It is employed in situations where a small number of mistakes is acceptable. In a hybrid structure adder, the estimated least significant bits (LSBs) and the accurate most significant bits (MSBs) are used in distinct regions. The fault is found in the summing of the LSB and the input carry of the MSB parts. This reduces the MSB part's error weight by limiting the carry input's error weight. Due to the fact that most of the work is done in the LSB section. Using pure approximation adder structures is the second strategy to consider. The major design requirements for these adders are to decrease power consumption and delay, as well as to lower the error probability of summing.

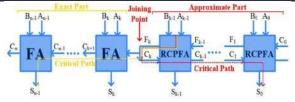

Hybrid adders with the usage of the RCPFA (approximate reverse carry propagate fulladder) will be studied in this work. The carry input is propagated from the high significant bit to the low significant bit in the approximation adder to generate the carry out. A prediction signal may be used as an output signal in this adder type, known as a reverse carry propagate adder (RCPA). The propagation weight will be reduced by adopting reverse carry propagation. Parallel prefix adder is used to add the MSB half because it may increase the speed of operation. An approximate reverse carry propagate adder is used to add the LSB half of the signal.

#### LITERATURE SURVEY

The Ripple carry adder (RCA) has the poorest power and area utilizations among the precise adder topologies. Despite this, there is a significant lag time. The precision of this adder has been compromised in order to boost the adder's energy economy and speed.

An error-tolerant adder structure (EAS), a rough approximation of an RCA, has been proposed. Figure 1 depicts the EAS organisational structure.

1. In this design, the input operands are seperated into 2 parts called exact

A Peer Reviewed Open Access International Journal

www.ijiemr.org

computation part and inexact computation part. In the exact part is the MSB part, the conventional FAs with a zero input carry for the each part are used wherease the inexact part is the LSB part which consists of a carry-free addition part.

Fig.1 Error tolerant adder structure

We chose an adder that employs reverse carry propagation, in which the carry is propagated in the opposite direction of the clock, because of the added delay imposed by carry propagation.

The standard FA, a critical building block of reverse carry propagate adders, has three equally weighted inputs. For a summation, it has a single output with twice the weight of the inputs and two outputs with the same weight as the inputs. Carry propagation delay (tCP) is an important timing component in FAs since it has historically played a role in defining the critical route delay in multibit adders (and multipliers). Short-delay violations might result in a large amount of error since the fault arises on the MSBs of the summation.

This is the result of the propagation and generation of the input carry of the MSBs through less significant bit FAs. Due to this reason, if the order of the carry propagation is reversed, one can see the decrease in the amount of error due to the timing violation.

#### 2. Reverse Carry Propagate Full-Adder Cell

Each exact FA generates its sum and carry output signals using

$$2C_{i+1} + S_i = A_i + B_i + C_i$$

.....(1)

Where Ai (Bi ) is the i<sup>th</sup> bit of the input A(B), Ci(Ci + 1) is the carry in (output), and Si is the i<sup>th</sup> bit of the sum.

Based on this equation, the output signals in the i<sup>th</sup> bit position relay on the i<sup>th</sup> bits of the inputs *A* and *B* and the carry out of the previous position (Ci ). By moving the term Ci (Ci + 1)to the left (right) of the equation, one can write as

$$S_i - C_i = A_i + B_i - 2C_{i+1} \qquad (2)$$

Considering equation (2), one can think of a full adder as a design whose operation depends on the carry out of the (i + 1)nth bit position (Ci + 1)and its input operand bits. For this structure, the sum and the carry signals having the equal weights are the outputs.

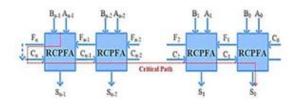

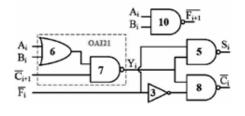

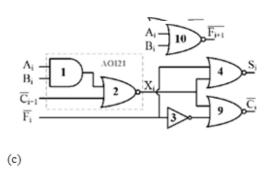

From the above discussion, we suggest a family of full adders for the RCPFA shown in Fig.

As shown in Fig. 2, these full adders have four inputs and 3 outputs. The inputs are the input operands (Ai and Bi), the carry out of the next bit position (Ci+1), and a forecast

A Peer Reviewed Open Access International Journal

www.ijiemr.org

signal (Fi). The RCPFA determines the carry (Ci), summation result (Si), and the forecast signal (Fi+1) as its output signals. As mentioned earlier, the advantage by using the RCPA is that the value of the error is in the direction with respect to decrease in the bit significance. This shows that the cumulative impact factor of the error (e.g., because of the delay variation) during the carry propagation is lower for bits with higher significances.

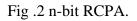

To determine a structure for RCPFA, the Karnaugh maps of the summation result  $(S_i)$  and carry  $(C_i)$  were drawn based on (2) and considering the forecast signal  $(F_i)$  as an input (Fig. 3) The Boolean equation between inputs gives rise to Si and Ci

Based on our design requirement we use 3 types of reverse carry propagate adders the designs of those adders is shown below. By using these proposed adders we can implement 3 types of reverse propagate adders and are it is used in the place of approximate adders which is shown on figure 1.

(a)

**(**b)

Fig.4 Internal structures of the (a) RCPFA-D1, (b) RCPFA-D2, (c) RCPFA -D3 The block diagram of an n-bit adder which is designed with the help of reverse carry propagate adder is shown in below figure As mentioned before, the weight of the carry decreases as the carry propagates in a counter-flow manner.

A Peer Reviewed Open Access International Journal

#### www.ijiemr.org

Fig.5 Architecture of an n-bit adder with RCPA This property helps having less vulnerability to the delay variation (due to process and supply voltage variations) impact for this adder when compared to other proposed approximate FAs. This is especially advantageous in the case of hybrid adders with large sizes for the approximate part which determines the critical path of the adder. The proposed RCPFAs may be used in hybrid adders whose general *n*-bit structure based on the RCPFAs is depicted in Fig. 8. Obviously, the design parameters of the adder.

#### **PROPOSED METHOD**

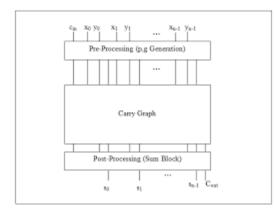

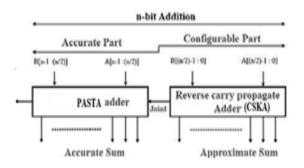

Here we will propose a new adder It is called as hybrid n-bit two n/2 bit adders are combined to generate an adder with an output of the same number of bits. We will employ a PASTA adder, a parallel selftimed adder, in order to increase delay performance. Carry, or how quickly the adder reaches each bit position, affects the delay in an adder. As a result, the carry chain is the most complex part of the design of binary addition. The carry chain's latency and length rise in tandem with the incoming operand's increase in breadth. Parallel prefix adders may be used to increase speed and reduce latency. Until all of the carry bits are calculated, simultaneous prefix adders compute a limited number of intermediate prefixes and then locate the big group prefixes. Operands A and B are added in three phases to a parallel prefix addition of width n:

- 1. Pre Processing

- 2. Carry Generation

- 3. Post processing

#### 1. Pre-processing stage:

In first stage process we compute, The generate signals and propagate signals are utilized such that carry in of each adder is generated. A and B are inputs.

It is one of the most extensively used and popular adders. This adder is used to conduct addition operations at a high rate of performance. Parallel prefix adders are a subset of this kind. PASTA adders are less expensive, but they also simplify wiring. It's like a tree structure that does the math. The Pasta adder has both grey and black cells. ' There will be one OR gate and two AND gates in every black cell. There is only one AND gate in every grey cell. A single AND gate and an OR gate are used to create the signal gi. Pi stands for propagate and just one AND gate is required. The term "carry generate" refers to the employment of one AND gate and one OR gate in the first black cell of the equation. This information may be seen in the equations 5 and 6.

$Pi = Ai Xor Bi \dots (5)$

A Peer Reviewed Open Access International Journal

$Gi = Ai. Bi \dots (6)$

Fig.6 Block Diagram of Parallel prefix addition.

#### 2. **Carry generation stage**:

We'll get the carries for every bit in this generating step. A parallel mode of execution is used. Carry computations in parallel are broken down into a number of smaller components. Two AND gates and one OR gate are included in the carry operator. Figures 7 and 8 show that the intermediate signals are propagate (Pi) and create (Gi).

$$P(i:k) = P(i:j) \cdot P(j-1:k) \dots \dots (7)$$

$$G(i:k) = G(i:j) + (G(j-1:k) \cdot P(i:j)) \dots \dots (8)$$

This carry can generated by using different cell structures such as Gray cell, Black cell and Buffer cell. By use of this cell structures we will be able to calculate final carry and is similar for all parallel prefix adders but the design of carry generation is different.

Fig.7 Black Cells, Gray Cells and Buffer cell used for carry generation stage.

www.ijiemr.org

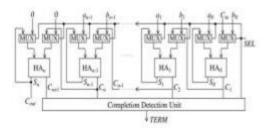

#### ARCHITECTURE OF PASTA

# Fig.8 Architecture of PASTA adder *1. Post Processing:*

The sum is generated either by the use of simple XOR gates or by the use of conditional sum adders. In conditional sum adders, for each bit position, It generates two tentative sums and the correct one will be selected when the relevant carry for that bit arrives.

Proposed Adder architecture is shown in below figure:

A Peer Reviewed Open Access International Journal

#### www.ijiemr.org

Fig.9 Modified Hybrid adder Architecture.

#### RESULT

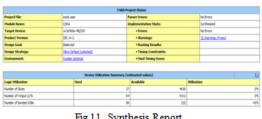

By implementing the adder by using two sub adders like PASTA adder and reverse carry propagate adder we can have better in terms of delay and energy. Here in this paper we present 32- bit adders with the design of reverse carry propagate adders. The results are presented in the below table

| S.No | 32 bit adder | Existing | Proposed |

|------|--------------|----------|----------|

|      |              | Method   | Method   |

| 1    | Area         | 95       | 112      |

| 2    | Delay        | 21.765   | 15.296   |

| 3    | power        | 5.521    | 4.485    |

|             |                                         | 0.001000499 ms                          |  |

|-------------|-----------------------------------------|-----------------------------------------|--|

| Name        | Value                                   | 0.001000497ms 0.001000498ms 0.001000    |  |

| ▶ 🍯 a[31.0] | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 |  |

| b[31:0]     | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 |  |

| 🔓 cin       | 0                                       |                                         |  |

| Ալ օր       | 0                                       |                                         |  |

| \$32.0]     | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 |  |

| lig d       | 0                                       |                                         |  |

| 16 e2       | 0                                       |                                         |  |

| li a        | 0                                       |                                         |  |

|             |                                         |                                         |  |

|             |                                         |                                         |  |

|             |                                         |                                         |  |

|             |                                         |                                         |  |

|             |                                         |                                         |  |

|             |                                         |                                         |  |

|             |                                         | X1: 0.001000499 ms                      |  |

. Fig.10. Simulation Results

Fig.11. Synthesis Report

#### CONCLUSION

Using two different kinds of adders, we were able to create an n-bit adder with a hybrid architecture. It is more important to employ approximation in addition's lower half since it is less significant than addition's upper half, where it is more crucial. The

pasta adder we utilised in this project is a parallel prefix adder, and the RCPA we built in this work is the approximation adder. We can save energy and improve latency by using this design.

#### REFERENCES

[1] Pashaeifar, M., Kamal, M., Afzali-Kusha, & Pedram, M. A., (2018).Approximate Reverse Carry Propagate Adder for **Energy-Efficient** DSP Applications. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 1– 12.

[2] Inumula Veeraraghava Rao. M.Aditya, K Sai Priyanka, S. Sai Rahul, P. Sathwik Approximate Reverse Carry Propagate Adder for Energy-Efficiency, International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-9, Issue-2, December 2019.

N. Zhu, W. L. Goh, W. Zhang, K. S. [3] Yeo, and Z. H. Kong, "Design oflow-power high-speed truncation-error-tolerant adder and its application in digital signal processing," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 18, no. 8, pp. 1225–1229, Aug. 2010.

S. Mittal, "A survey of techniques [4] for approximate computing," ACM Comput. Surv., vol. 48, no. 4, pp. 62-1-62-33, Mar. 2016.

A Peer Reviewed Open Access International Journal

www.ijiemr.org

[5] B. Zeydel, D. Baran, and V. Oklobdzija, "Energy- Efficient Design Methodologies: High- Performance VLSI Adders," IEEE Journal of Solid-State Circuits, vol. 45, no. 6, pp. 1220–1233, June 2010.

[6] A. Madanayakeet al., "Low-power VLSI architectures for DCT/DWT: Precision vs approximation for HD video, biomedical, and smart antenna applications," IEEE Circuits Syst. Mag., vol. 15, no. 1, pp. 25–47, 1st Quart., 2015.

[7] V. Gupta, D. Mohapatra, A. Raghunathan, and K. Roy, "Low-power digital signal processing using approximate adders," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 32, no. 1, pp. 124–137, Jan. 2013.

[8] Z. Yang, J. Han, and F. Lombardi, "Transmission gate-based approximate adders for inexact computing," in Proc. IEEE/ACM Int. Symp. Nanosc. Archit. (NANOARCH), Jul. 2015, pp.145–150.

[9] H. R. Mahdiani, A. Ahmadi, S. M. Fakhraie, and C. Lucas, "Bio-inspired imprecise computational blocks for efficient VLSI implementation of soft-computing applications," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 57, no. 4, pp. 850–862, Apr. 2010.

[10] B.Mounika, and Dr.A. RajKumar, " Design of Efficient 32-Bit Parallel Prefix Brent Kung Adder," Advances in Computational Sciences and Technology ISSN 0973-6107 Volume 10, Number 10 (2017) pp. 3103-3109.

[11] Potdukhe, P. P., & Jaiswal, V. D. (2016). Design of high speed carry select adder using brent kung adder. 2016 International Conference on Electrical, Electronics, and Optimization Techniques (ICEEOT).

#### **AUTHORS PROFILE**

**T Sai Karthik** is pursuing Mtech in Holy Mary Institute of Technology & Science, Keesara, Bogaram, Ghatkesar Rd, Kondapur,

Telangana 501301. His interest areas is VLSI

M Sunder Rao, M.Tech working as Assistant professor ,in the Department of Electronics and communication Holy

Mary Institute of Technology and Science, Hyderabad.