A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **COPY RIGHT**

2019IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 4<sup>th</sup> Sept 2019. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-08&issue=ISSUE-09

Title REDUCED CARRIER PWM SYSTEM WITH UNITED LOGICAL FOR REDUCED SWITCH COUNT MULTILEVEL INVERTERS

Volume 08, Issue 09, Pages: 393-401.

**Paper Authors**

#### E SAMYUKTHA, M LAXMI PRASANNA, CH NAVYA

Anu Bose Institute of Technology K.S.P Road, New paloncha, Bhadradri Kothagudem, Telangana, India

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

## REDUCED CARRIER PWM SYSTEM WITH UNITED LOGICAL FOR REDUCED SWITCH COUNT MULTILEVEL INVERTERS

E SAMYUKTHA<sup>1</sup>, M LAXMI PRASANNA<sup>2</sup>, CH NAVYA<sup>3</sup>

1,2,3 **UG Students,** Dept. of Electrical and Electronics Engineering Anu Bose Institute of Technology KSP Road, Newpaloncha, BhadradriKothagudem, Telangana, India.

eesamyuktha@gmail.com<sup>1</sup>, laxmiprasannamugithi56@gmail.com<sup>2</sup>, navyachelimala818@gmail.com<sup>3</sup>

**Abstract:** The imperative decline inswitch check of symmetrical/uneven reduced switch count amazed inverters(RSCMLI) topologieshas changed the action of inverter with the ultimate objective that the standard conveyor based heartbeat width change (PWM) plans, for instance, level-moved PWM and stage moved PWM canno more recognize them. To controlthese RSC-MLItopologies, diminished transporter PWMplans with balanced trading method of reasoning expanded increasingly observable quality. These plans incorporate sensible reliable enunciations to comprehend the trading states oftheinverter. Regardless, these reasonable explanations vary with topological strategy and number of levels. Likewise, these plans producehigh complete consonant bending (THD) in linevoltages. Along these lines, toimprove the line-voltageTHD and entirety up the trading reason, a balanced diminished conveyor PWMplot with bound together reliable explanations is shown here. The proposed PWMplan is really generous forany topology and canbe adequately flexible to any number of levels in the inverters. To endorse the utilization oftheproposedPWM to control anyRSC-MLI, preliminary examinations of various amiss RSC-MLI topologies with the proposed PWMplan are finished. Further, to affirm the pervasiveness oftheproposed arrangement with respect to THD, multifaceted design, flexibility, and estimation load, its introduction is differentiated and conveyor based PWM plans point by point in the composition.

#### 1. INTRODUCTION

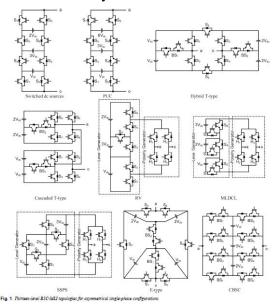

The interest for diminishing the sizeof staggered inverters (MLI)has prompted another area ofMLIs, named as decreased switch tally (RSC)MLIs[1]. Contingent desource voltage proportions, upon theseRSC-MLIs are named symmetrical and topsy-turvy. With deviated desource voltages, further decrease inswitch tally canbe accomplished. A few RSC-MLI topologies, for example, staggered dc

interface(MLDCL)[2], pressed U-cell (PUC) [3], fellbi-polar exchanged cells (CBSC) [4], invert voltage (RV) [5], exchanged dc sources [6], essential unit MLI [7], envelopetype(E-type)[8],T-type half breed T-type arrangement associated exchangedsources(SCSS), exchanged arrangement parallelsources (SSPS) settledMLI, exchanged capacitor unit decreased fell & different topologies are

A Peer Revieved Open Access International Journal

www.ijiemr.org

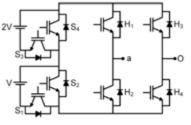

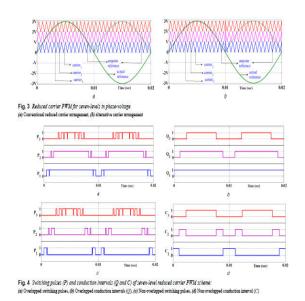

inthe writing. InFig.1 accounted for demonstrates the circuit setup of different single-stage 13-level lopsided RSCtopologies, for example, exchanged desources, PUC, fell T-type, cross breed Ttype, CBSC, SSPS, RV, MLDCL, and Etype. Among the beat width tweak (PWM) plans reportedfor MLIs, transporter based plans, for example, level-moved PWM (LSPWM) and stage moved (PSPWM) are the least difficult because of their ease in implementaThese PWM plans can understand inverter exchanging states in which gadgets directing for accomplishing lowerlevels stay in conductionat higherlevels also. This went about as an impediment of the traditional transporter based plans to acknowledge RSC-MLIs, topologies since these has restricted redundancies and have the exchanging activity where the lower level conduction gadgets may not stay in conduction at higher level.In the writing, different regulation plans are accounted for controlling symmetrical and deviated **RSC-MLI** designs. Among them, half breed PWM is one of the prevalent plans for executing awry fell topologies, for example, Cascade H-bridgeThis plan can likewise be actualized to non-fell topologies, for example, SSPS by including an extra Hconnect in each stage In this plan, estimation or estimation of yield voltage of the higher voltage connect/units is important, to infer the reference signal for the lower voltage connect/units. Henceforth, any slack or blunders in the estimation or estimation will affect the yield voltage. PWM plans, for example, particular consonant end [8] and space vector are accounted for E-type, PUC, settled cell, and different three-stage RSC topologies. These exchanging plans can be summed up to higher levels, yet requires subtle estimations to get exchanging instants. Switching plans utilizing lowrecurrence bearer (50 or 100 Hz) with and legitimate administrators without accounted for different RSC MLIs, for example, MLDCL, CBSC, fundamental unit MLI, T-type, and half breed T-type These low-recurrence PWM plans brings about lower request sounds and poor THD. To get better THD and diminish the multifaceted nature in usage, different novel PWM plans are accounted for. Multi-reference tweak plan is one of such plan revealed for T-type, fell T-type, and couple of other fell topologies. This plan can be appropriate to any MLI with any number of levels, yet this plan results high THD in line-voltages .Switching capacity PWM is the other famous plan detailed for PUC, exchanged dc sources, and crossover T-type topologies. To get the exchanging beats, this plan builds up a crossover capacity utilizing least and greatest points of confinement of every bearer. In this manner, to understand these bearer limitations, controller requires various comparators, which builds the unpredictability at higher levels.Reduced transporter PWMis the other prominent PWM, which includes a unipolar tweaking and level-moved transporter signals. In this produced plan, beats are straightforwardly contrasting reference and its bearers and further worked with client

A Peer Revieved Open Access International Journal

www.ijiemr.org

characterized intelligent articulations to get wanted changing heartbeats to control the inverter. Notwithstanding, these legitimate articulations shift with topological game plan and number of stage voltage levels. Further, this ordinary diminished bearer course of action results high THD in linevoltage. Consequently, an other regulating signal and diminished bearer course of action is reported. The exchanging rationale of this plan includes least and greatest limitations of every transporter to get wanted activity.

Notwithstanding, it is to be noted that reduced transporter PWM plans with summed up intelligent articulations are the least difficult and a lot simpler to actualize contrasted with exchanging plan including bearer least and most extreme constraints. By exploring the different adjustments of RSC-MLI topologies, the accompanying ends can be drawn

Among the adjustment plans detailed for RSC-MLIs, decreased bearer PWM plot

- with sensible articulations are the easiest. Be that as it may, these legitimate articulations are not summed up and differ with inverter topology and number of levels.

- Conventional diminished transporter PWM plan results debased line THD execution, as its bearer course of action is like LSPWMinverse stage attitude (OPD). Consequently, in this paper, an altered diminished bearer PWM plot with summed up intelligent articulations is proposed, to such an extent that the proposed exchanging rationale can control any RSC-MLI regardless to the voltage proportions and topological course of action. To determine these bound together sensible articulations, constraints of ordinary decreased bearer tweak conspire in controlling **RSC-MLI** topologies investigated. To confirm the effectiveness of proposed **PWM** conspire, presentation in controlling different 13-level unbalanced RSCMLI topologies is explored. Further, to guarantee the predominant presentation of the proposed plan, a far reaching test correlation with best in class plans revealed in the writing is exhibited. This paper is spread out as pursues: Section 2 explores the impediments of customary diminished transporter tweak plans and displays the need of bound together legitimate articulations to acknowledge RSC-MLI topologies. Area 3 shows the approach of the proposed plan deduction of bound together coherent articulations. Trial execution of proposed plan to different RSC topologies is talked about in Section 4.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Seven-level single-phase configuration of RSC-MLI-based MLDCL

#### 2. Methodology and implementation of the proposed modulation scheme

To determine a brought together rationale articulation for getting non-covered interim (C) from the covered interim (Q), the nature of both these conduction interims ought to be broke down. Fig. 5 (got from Figs. 4b) and d) demonstrates the conduction interims Q and C together. This figure deduces that the ideal conduction interim Ccan be acquired by playing out an intelligent activity on Q with its adjoining groups. From Fig. 5a, by watching Q3 and C3 uncovers their indistinguishable nature of exchanging and consequently

$$C3 = Q3 \qquad (2)$$

In any case, Q2 and C2 are unique in relation to one another and from Fig. 5b, the accompanying connections are gotten.

If

$$Q_3 = 0$$

and  $Q_2 = 0$ , then  $C_2 = 0$ ;

if  $Q_3 = 1$  and  $Q_2 = 1$ , then  $C_2 = 0$ ;

if  $Q_3 = 0$  and  $Q_2 = 1$ , then  $C_2 = 1$ .

It ought to be noticed that Q3 = 1 and Q2 =0 case does not show up as lower conduction interim Q2 consistently stays high when upper conduction interim Q3 is high. To get an intelligent connection for C2 as far as Q3 and Q2, a two-variable Karnaugh-map (K-map) is actualized in Fig. 5b. From Fig. 5b, consistent connection for C2 is gotten as C2 = Q3Q2. To understand this rationale in equipment, two rationale entryways NOT AND are required. To lessen these rationale doors, a couldn't care less factor is incorporated into K-map and the intelligent connection (3) is acquired, which requires an Ex-OR entryway as it were

$$C_2 = \bar{Q}_3 Q_2 + Q_3 \bar{Q}_2 = Q_2 \oplus Q_3$$

(3)

To obtain conduction interval  $C_1$ , Fig. 5c is considered and following relationships are obtained. If  $Q_2 = 0$  and  $Q_1 = 0$ , then  $C_1 = 0$ ; if  $Q_2 = 1$  and  $Q_1 = 1$ , then  $C_1 = 0$ ;

if  $Q_2 = 0$  and  $Q_1 = 1$ , then  $C_1 = 1$ .

With the help of K-map shown in Fig. 5c, logical relation (4) is obtained for conduction interval  $C_1$

$$C_1 = Q_1 \oplus Q_2 \tag{4}$$

Generalising (2)-(4), (5) can be obtained, where i is the carrier number

for

$$i = (n-1)/2$$

$C_i = Q_i$

for  $1 \le i < (n-1)/2$

$C_i = Q_i \oplus Q_{i+1}$

(5)

Applying the beat Pi (|ref|>carrieri) over the interim Ci brings about wanted non-covered exchanging beats. This exchanging activity of the proposed balance plan to control seven-level inverter is appeared in Fig. 6.In Fig. 6, C3 should be dynamic to getting

A Peer Revieved Open Access International Journal

www.ijiemr.org

voltage band of 3 V to 2 V. So also, C2 and C1 should be dynamic for getting voltage band of 2 V to V and V to 0, individually. C3 high with P3 high, for example beat C3P3 is in charge of getting 3 V voltage state. C3 high with P3 low or C2 high with P2 high, for example beat C3P<sup>-</sup>3 + C2P2 acquires 2 V voltage state. Correspondingly, C2 high with P2 low or C1 high with P1 high, for example C2P<sup>-</sup>2 + C1P1 brings about V voltage state. C1 high with P1 low, for example beat C1P-1results in zero voltage. The extremity of these voltage states is chosen by the extremity of the adjusting signal, where positive voltage levels are acquired for the positive portion of the reference and negative voltage levels are gotten for negative portion of the balancing signal. Table 1 demonstrates the execution of the proposed changing rationale to understand a seven-level inverter topology appeared in Fig. 1. For instance, to acquire +3 V voltage level, switches H4, S1, S3, and H1 ought to be in conduction. In this manner, these switches are connected with heartbeat C3P3 for the positive portion of the reference. Also, to acquire -3 V voltage level, beat C3P3 connected to switches H2, S1, S3, and H3 for the negative portion of the reference. A comparative clarification holds useful for outstanding voltage level as displayed in Table - 1.In this proposed plan, the acquired number of wanted pulseswill be equivalent to the quantity of stage voltage levels, where eachpulse is in charge of getting a specific voltage level. Further, every one of these ideal heartbeat will be given to the gadgets

(of the thought about inverter) to be in conduction to accomplish the separate voltage state. Further, summing up these got exchanging beats for higher voltage levels (6) is acquired

for

$$\frac{n-1}{2}V$$

$\Rightarrow$  switching pulse  $= C_{\frac{n-1}{2}}P_{\frac{n-1}{2}}^{n-1}$

for  $V \le iV \le \left(\frac{n-1}{2}-1\right)V$  (6)

$\Rightarrow$  switching pulse  $= C_{i+1}\bar{P}_{i+1} + C_{i}P_{i}$

for  $0V$

$\Rightarrow$  switching pulse  $= C_{1}\bar{P}_{1}$

Fig. 6 Implementation of the proposed PWM scheme for seven-level phase-voltage

| Polarity generation | Voltage level | Switching pulse           | Devices to be in on to obtain the respective voltage level in Fig. 2 |  |  |  |  |

|---------------------|---------------|---------------------------|----------------------------------------------------------------------|--|--|--|--|

| ref≥0               | +3 V          | $C_3P_3$                  | H <sub>4</sub> -S <sub>1</sub> -S <sub>3</sub> -H <sub>1</sub>       |  |  |  |  |

|                     | +2 V          | $C_3P_3 + C_2P_2$         | H <sub>4</sub> -S <sub>2</sub> -S <sub>3</sub> -H <sub>1</sub>       |  |  |  |  |

|                     | +V            | $C_1\tilde{P}_2 + C_1P_1$ | H4-S1-S4-H1                                                          |  |  |  |  |

| for zero-level      | 0             | $C_1\bar{P}_1$            | H4-S2-S4-H1 or H2-S2-S4-H3                                           |  |  |  |  |

|                     | -             | -                         |                                                                      |  |  |  |  |

| ref < 0             | -V            | $C_2\tilde{P}_2 + C_1P_1$ | H2-S1-S4-H3                                                          |  |  |  |  |

|                     | -2 V          | $C_3P_3 + C_2P_2$         | H <sub>2</sub> -S <sub>2</sub> -S <sub>3</sub> -H <sub>3</sub>       |  |  |  |  |

|                     | -3 V          | $C_3P_3$                  | H2-S1-S3-H3                                                          |  |  |  |  |

| Circuit/parameter                               | Component/value                                                       |  |  |  |  |

|-------------------------------------------------|-----------------------------------------------------------------------|--|--|--|--|

| 30 V isolated dc power supplies (12 no.)        | 30 V, 3 A dual channel regulated power supply                         |  |  |  |  |

| 13-level asymmetrical RSC-MLI                   | developed using 2 modules of generalised converter with 24 IGBTs each |  |  |  |  |

| IGBT model and rating                           | IKW40T120, 40 A and 1200 V                                            |  |  |  |  |

| carrier frequency (f <sub>cr</sub> )            | 2 kHz                                                                 |  |  |  |  |

| amplitude modulation index (m <sub>a</sub> )    | 0.98                                                                  |  |  |  |  |

| load                                            | three-phase star-connected 1 kW 0.85 power factor lagging.            |  |  |  |  |

| controller (to obtain firing signals for IGBTs) | dSPACE micro-lab box RTI1202 R&D controller sampling time (20 µs)     |  |  |  |  |

# 4. Implementationofthe proposed scheme to 13-levelasymmetrical RSC-MLItopologies

The presentation of the proposedPWM plan is approved creating trial set-ups of various 3-stage IGBTbased 13-level unbalanced RSC-MLItopologies. The created topologiesare MLDCL, SSPS, exchanged

A Peer Revieved Open Access International Journal

www.ijiemr.org

dcsources, half and half T-type&E-type (as appeared in Fig. 1). Further, to approve the predominance of theproposed conspire, the above chose topologiesare likewise controlled utilizing customary diminished transporter **PWM** plot. Distinctive inverter topologies are created by utilizing twoinverter modules with 24 individual IGBTsin each. The balance plans indSPACE Micro-lab are executed boxRTI1202 R&Dcontroller. The transporter signalrecurrence and regulation file (mama) abundancy chosen as2kHzand0.98, separately. The dc info sourcevoltage (Vdc) is chosen as 30Vandwith this, the greatest adequacy of stage voltage is 180V. The total rundown ofparameters utilized in test study is given in Table 2 and the photo of the exploratory setup is appeared in Fig. 7. Table 3 demonstrates the usage oftheproposed changing rationale understandthesechose RSC-MLI topologies. Fig. 8 demonstrates the exploratory exhibition of stage voltages and their relating consonant spectra. Figs. 8a-eshow the stage voltage execution of 13level MLDCL,SSPS, exchanged dc sources, T-type,&E-typehilterkilter mixture topologies withthe proposed PWM conspire. Fig.8f delineates the stage voltageexecution of13-level MLDCL with traditional decreased transporter **PWM** plot. Correspondingly, Fig. 9 delineates the test line-voltage execution of these RSC topologies with the proposed PWM plan and traditional diminished bearer conspire. Line-voltages and their comparing symphonious spectra of the proposed plan

for considered13-level filter kilter topologies are appeared in Figs. 9a–e. Fig. 9f portrays the line-voltage performance of13-level MLDCL with traditional decreased transporter PWM plot.

Fig. 7 Photograph of the experimental set-up for realising 13-levelasymmetrical switched dc source inverter

| Polarity generation | Level | Switching pulse             | Devices to be in conduction to obtain the respective voltage level |                |                                                                |               |           |  |  |

|---------------------|-------|-----------------------------|--------------------------------------------------------------------|----------------|----------------------------------------------------------------|---------------|-----------|--|--|

|                     |       |                             | MLDCL                                                              | SSPS           | Switched dc sources                                            | Hybrid T-type | E-type    |  |  |

| ref≥0               | +6 V  | $C_0P_0$                    | H4-S1-S3-S5-H1                                                     | H4-S2-S5-H1    | S2-S3-S6-S7                                                    | S2-S6-S1      | S1-S4-S5  |  |  |

|                     | +5 V  | $C_0\tilde{P}_6 + C_2P_5$   | H4-S2-S3-S5-H1                                                     | H4-S1-S5-H1    | S1-S3-S6-S7                                                    | S2-S6-BS1     | BS1-S4-S5 |  |  |

|                     | +4 V  | $C_2\tilde{P}_5 + C_4P_4$   | H4-S1-S4-S5-H1                                                     | H4-S2-S4-H1    | S2-S3-S6-S8                                                    | BS2-S6-S1     | S2-S4-S5  |  |  |

|                     | +3 V  | $C_4\bar{P}_4+C_3\bar{P}_3$ | H4-S1-S3-S6-H1                                                     | H4-S1-S4-H1    | S <sub>1</sub> -S <sub>3</sub> -S <sub>6</sub> -S <sub>8</sub> | BS2-S6-BS1    | S1-BS2-S5 |  |  |

|                     | 2V    | $C_2P_3 + C_2P_2$           | H4-S2-S3-S6-H1                                                     | H4-S1-S6-H1    | S2-S4-S6-S7                                                    | S4-S6-S1      | S1-S4-S6  |  |  |

|                     | V     | $C_2\bar{P}_2 + C_1P_1$     | H4-S1-S4-S6-H1                                                     | H4-S3-S6-H1    | S2-S3-S5-S7                                                    | S4-S6-BS1     | BS1-S4-S6 |  |  |

| for zero-level      | 0     | $C_1\tilde{P}_1$            | H4-S2-S4-S6-H1 or                                                  | H1-H3 or H2-H4 | S1-S3-S5-S7                                                    | S4-S6-S3      | S1-S3-S5  |  |  |

|                     |       |                             | H2-S2-S4-S6-H3                                                     |                |                                                                |               |           |  |  |

| ref< 0              | -V    | $C_2P_2 + C_1P_1$           | H2-S1-S4-S6-H3                                                     | H2-S3-S6-H3    | S1-S4-S6-S8                                                    | S2-S5-BS1     | BS1-S3-S5 |  |  |

|                     | -2V   | $C_1\bar{P}_3 + C_2P_2$     | H2-S2-S3-S6-H3                                                     | H2-S1-S6-H3    | S1-S3-S5-S8                                                    | S2-S5-S3      | BS1-BS2-S |  |  |

|                     | -3 V  | $C_4\bar{P}_4+C_3\bar{P}_3$ | H2-S1-S3-S6-H3                                                     | H2-S1-S4-H3    | S2-S4-S5-S7                                                    | BS2-S5-BS1    | S2-BS2-S6 |  |  |

|                     | -4 V  | $C_3\bar{P}_5 + C_4P_4$     | H2-S1-S4-S5-H3                                                     | H2-S2-S4-H3    | S1-S4-S5-S7                                                    | BS2-S5-S3     | S1-S3-S6  |  |  |

|                     | -5V   | $C_sP_6 + C_sP_5$           | H2-S2-S3-S5-H3                                                     | H2-S1-S5-H3    | S2-S4-S5-S8                                                    | S4-S5-BS1     | BS1-S3-S6 |  |  |

|                     | -6 V  | $C_{o}P_{o}$                | H2-S1-S3-S5-H3                                                     | H2-S2-S5-H3    | S1-S4-S5-S8                                                    | S4-S5-S3      | S2-S3-S6  |  |  |

So as assess the entire inverter framework, itis important demonstrate the presentation of the inverter flows. Fig10 delineates the exploratory line-current execution of RSC topologies with proposed and customary decreased bearer PWM plans for three-stage star-associated load.Line-current and their comparing consonant spectraofthe proposed plan forconsidered 13-level topsy-turvy topologies are appeared in Figs. 10a—e. Fig. 10f portrays the line-current execution of

A Peer Revieved Open Access International Journal

www.ijiemr.org

13level MLDCLwith customary diminished bearer PWM scheme. Inaviewto appraise the adequacy of the proposed PWM conspire, a far reaching correlation is completed transporter based PWM plans revealed in the writing. Forthis, the PWM conspire alongside theinverterrevealed in the writing executed tentatively contrasted and the proposed PWM plot regarding consonant execution, multifaceted nature in usage, and calculation load. The synopsis of benefits and negative marks are introduced in Table 4. Looking at Figs. 8–10 alongside Table 4, the accompanying ends are inferred.

- a) From Figs. 8a–e, it is seen that all the stage voltagewaveforms and their symphonious spectraare indistinguishable with predominant consonant showed up at recurrence adjustment list (mf=40).

- b) Comparing Fig. 8f with Figs. 8a–e, it very well may be seen that THD estimations of customary decreased transporter plot (6.1%) are less when contrasted and the proposed plan (7.8%). By the by, the customary decreased transporter PWM conspire

- c) haslessTHD esteem however its sideband music are unique and focused at mf. Thesizeofthe music is likewise extraordinary in the two techniques, which prompts huge contrast inline-voltageTHD.

- Theline-voltagewaveformsandtheir d) relating consonant spectra withtheproposedPWM plan appeared in Figs. 9a-eare indistinguishable as far symphonious waveform shapeand **THDare** execution. The acquired

- indistinguishable withside-band music focused atmf=40.

- e) ComparingFigs. 9a—e withFig. 9f, it very well may be seen thatthe proposed plan producesimproved symphonious execution (2.8%)when contrasted and regular diminished bearer PWM plot (6.0%). The explanation behind this is theproposed PWM plan willhelpforbetter wiping out music displayed in stage voltages.

- Fromline-current execution appeared in Fig. 10, it is seen that line-current waveformsand their comparing symphonious spectra withthe proposed PWM plan are indistinguishable as far as waveform shapeand consonant execution. It can likewise be seen that the proposed plan producesimproved consonant execution (2.3%)when contrasted and ordinary decreased bearer PWM plan line-flows (5.4%) appeared in Fig. 10f.

Fig. 9 Line-voltage waveforms and their corresponding harmonic spectra (scale: X-axis: 10 ms/div and Y-axis: 100 V/div (a) MLDCL (b) SSPS, (c) Switched de sources, (d) Hybrid T-type, (d) MLDCL with conventional reduced carrier PWM

A Peer Revieved Open Access International Journal

www.ijiemr.org

- i. Theproposed plan canbe straightforwardly pertinent toany MLI topologyand effectively versatile to higher numberoflevels independent oftopological course of action and devoltage proportions.

- Theproposed PWM plan produces improvedlineTHD . execution contrasted and regular diminished bearer andmulticarrier **PWM** plans and comparative execution THD when contrasted and exchanging capacity PWM plot.

- iii. The turnaroundtime for execution ofthe proposed PWM I. plan is altogether diminished andremains practically invertertopology. Theless calculation weight ofthe proposed plan will enable the controller to precisely execute higher exchanging frequencies.

#### **Conclusion**

To defeat the impediments of traditional decreased bearer PWM conspire, this paper displayed a changed diminished transporter PWM plot with brought together legitimate articulations. The adequacy of the proposed exchanging rationale is approved with test ponders on different 13-level hilter kilter RSC-MLItopologies. Further, unrivaled

execution oftheproposed plan confirmed by contrasting its presentation and traditional transporter **PWM** plans. Topologyautonomous activity, streamlined changing rationale speculation to higherlevels, less weight, calculation and improvedlinevoltageTHD execution of the proposed decreased bearer PWMplan fills in asa feasible answer for defeat the negative marks of ordinary multicarrier, diminished transporter, and multireference PWM plans.

| Carrier-based P                                    | WM scheme and top                                        | pology reported in the literature |                            | With the proposed PWM<br>scheme |                             |                           | Merits and demerits of<br>PWM scheme reported |                                                                                                                                                                                                 |

|----------------------------------------------------|----------------------------------------------------------|-----------------------------------|----------------------------|---------------------------------|-----------------------------|---------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWM scheme                                         | Topology                                                 | Phase-<br>voltage<br>THD, %       | Line-<br>voltage<br>THD, % | Turnaround<br>time, µs          | Phase-<br>voltage<br>THD, % | Line-<br>voltage<br>THD % | Turnaround time, µs                           | in the literature                                                                                                                                                                               |

| multi-reference<br>[11, 13, 23, 25]                | T-type seven-level<br>[11]                               | 15.7                              | 14.8                       | 6.5                             | 15.7                        | 4.9                       | 6.2                                           | ✓ require less computational time                                                                                                                                                               |

|                                                    |                                                          |                                   |                            |                                 |                             |                           |                                               | ✓ scalable to higher level ✓ directly applicable to a topologies                                                                                                                                |

|                                                    |                                                          |                                   |                            |                                 |                             |                           |                                               | X high line-voltage THD<br>X difficulty in implement<br>for closed-loop application                                                                                                             |

|                                                    |                                                          |                                   |                            |                                 |                             |                           |                                               | due to the presence of<br>multiple references                                                                                                                                                   |

| reduced carrier<br>with logic gates<br>[9, 10, 27] | modified T-type<br>seven-level [10]                      | 15.8                              | 15.0                       | 19                              | 15.6                        | 4.8                       | 5.9                                           | k high line-voltage THD     switching logic is     complex and requires more     computational time                                                                                             |

|                                                    |                                                          |                                   |                            |                                 |                             |                           |                                               | X neither scalable nor directly applicable to all topologies                                                                                                                                    |

| switching function<br>PWM [5, 16]                  | symmetrical seven-<br>level switched dc-                 | 15.6                              | 4.8                        | 7.5                             | 15.5                        | 4.7                       | 6.0                                           | ✓ good line-voltage THE performance                                                                                                                                                             |

|                                                    | sources [6]                                              |                                   |                            |                                 |                             |                           |                                               | ✓ scalable and applicabl<br>to all toplogies<br>X involves large number<br>comparators which<br>occupies more memory<br>and requires more<br>computation time to realis<br>the switching pulses |

| reduced carrier<br>[5]                             | RV seven-level [5]                                       | 15.7                              | 14.9                       | 5.3                             | 15.6                        | 4.8                       | 6.1                                           | <ul> <li>scalable with simplifie<br/>switched logic and takes<br/>very less computational<br/>time</li> </ul>                                                                                   |

|                                                    |                                                          |                                   |                            |                                 |                             |                           |                                               | x not applicable to all<br>topologies x high line-voltage THE                                                                                                                                   |

| hybrid PWM [17,<br>20, 22, 32]                     | asymmetrical SSPS<br>with H-bridge eleven-<br>level [17] | 9.9                               | 3.1                        | 6.6                             | 9.6                         | 3.0                       | 7.2                                           | ✓ good line-voltage THE<br>performance                                                                                                                                                          |

|                                                    | ievei [17]                                               |                                   |                            |                                 |                             |                           |                                               | <ul> <li>scalable and possess<br/>simplified switched logic<br/>and takes very less<br/>computational time</li> <li>x applicable only to<br/>asymmetrical cascaded<br/>topologies</li> </ul>    |

|                                                    |                                                          |                                   |                            |                                 |                             |                           |                                               | x may involve mixed<br>switching frequencies,<br>hence may produce<br>unwanted voltage spikes<br>phase and line-voltages                                                                        |

#### REFERENCES

- 1. Gupta,K.K.Ranjan,A.Bhatnagar, P., et al.: 'Staggered inverter topologies with decreased gadget check: an audit', IEEE Trans. Power Electron., 2016, 31, (1), pp. 135–151

- 2. Su,G.-J: 'Staggered DC-connect inverter', IEEE Trans. Ind. Appl., 2005, 41,pp. 848–854 Sanjeevan, A.R., Kaarthik, R.S., Gopakumar, K., et al.: 'Decreased commonmode voltage activity of another

A Peer Revieved Open Access International Journal

www.ijiemr.org

seven-level half breed staggered inverter topology with a solitary DC voltage source', IET Power Electron., 2016, 9, (3), pp. 519–528

- 3. Babaei, E.: 'A course staggered converter topology with decreased number of switches', IEEE Trans. Power Electron., 2008, 23, (6), pp. 2657–2664

- 4. Najafi, E., Yatim, A.H.M. 'Plan and execution of another staggered inverter topology', IEEE Trans. Ind. Electron., 2012, 59, (11), pp. 4148–4154

- 5. 6.Gupta,K.K.Jain,S.: 'An epic staggered inverter dependent on exchanged DCsources', IEEETrans. Ind. Electron., 2014,61,(7), pp.3269–3278

- 6. Babaei, E., Laali, S., Bayat, Z.'A solitary stage fell staggered inverter dependent on another essential unit with decreased number of intensity switches', IEEE Trans. Ind. Electron., 2015, 62, (2), pp. 922–929

- 2015,62,(2),pp.922–929 7 Samadaei F. Gho

- 7. Samadaei, E., Gholamian, S.A., Sheikholeslami, An., etal.: 'An envelope type (E-type) module: uneven staggered inverters with diminished parts', IEEE Trans. Ind. Electron., 2016, 63, (11), pp. 7148–7156

- 8. Park,S.-J.,Kang,F.-S,Lee,M.H.etal.: 'another single-stage five-level PWMinverter utilizing a killjoy control plot', IEEETrans.Power

Electron.,2003,18,(3),pp.831–843

9. Choi, J.-S., Kang, F.-S: Seven-level PWM inverter utilizing series connected capacitors paralleled to a solitary DC voltage source', IEEETransIndElectron.,2015,62,(6), pp.3448–3459

- 10. Rahim,N.A.Chaniago,K.Selvaraj,J.: 'Single-stage seven-level gridconnected inverter for photovoltaic framework', IEEETrans.IndElectron.,2011,58, (6), pp.2435–2443

- 11. Alishah,R.S.,Nazarpour,D.,Hosseini, S.H.,etal.'Decrease of intensity electroniccomponents in staggered converters utilizing another course structure',IEEETrans.Ind.Electron., 2015, 62, (1), pp. 256–269.