A Peer Revieved Open Access International Journal

www.ijiemr.org

#### **COPY RIGHT**

2019IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 4<sup>th</sup> Sept 2019. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-08&issue=ISSUE-09

Title GRID-TIE METHOD SHORT MECHANISMS 9-LEVEL DROPPED-TRANSFORMER MULTILEVEL INVERTER SUBSTANTIATION

Volume 08, Issue 09, Pages: 419-434.

**Paper Authors**

#### M ROJA, K VENKATA LAXMI, P CHAMUNDESWARI

Anu Bose Institute of Technology K.S.P Road, New paloncha, Bhadradri Kothagudem, Telangana, India

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic

Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

#### GRID-TIE METHOD SHORT MECHANISMS 9-LEVEL DROPPED-TRANSFORMER MULTILEVEL INVERTER SUBSTANTIATION

M ROJA<sup>1</sup>, K VENKATA LAXMI<sup>2</sup>, P CHAMUNDESWARI<sup>3</sup>

<sup>1,2,3</sup>UG Students, Dept. of Electrical and Electronics Engineering Anu Bose Institute of Technology KSPRoad, NewPaloncha, Bhadradri Kothagudem, Telangana, India. rojam773@gmail.com<sup>1</sup>, venkatlaxmi268@gmail.com<sup>2</sup>, chamundeswaripramkasham66@gmail.com<sup>3</sup>

**Abstract:** - The fundamental issue identified with fell H-connect cells staggered inverters (CHBs) is their utilizing of an enormous number of parts, for example, switches and DCsources. Along these lines, minimization of segments in these sorts gadgets is critical. Fell transformers staggered inverters (CTMIs) have totally killed the requirement for a few DCsources in CHBs. Accordingly, minimization of different segments in CTMIs can prompt acquire upgraded structure for staggered inverters. The present article presents a basic and minimized structure for transformer based staggered inverters. Sincethe quantity of used segments in the proposed structure is astoundingly decreased, thecost, volume and unpredictability are limited. The presentation of the proposed inverterhasbeen examined through two unique methodologies. Right off the bat, it is tried under state of providing a neighborhood load, and furthermore, utilizing test based current control methodology, its presentation is reviewed whenbeing associated with the network. In the last test the spillage inductances of the transformers are used to execute the example based current control technique, in this manner, the requirement for additional channel is destroyed. The achievability of the proposed topology has been approved by utilizing research facility manufactured model alongside a PC help recreated models.

**Index Terms:** -multilevel inverter, ComponentReduction, GridConnectedConverter, Sample BasedCurrentControl.

#### 1. INTRODUCTION

Multilevel inverters haverecently been pulling expanding measure consideration. The primary preferences of these sorts of devises are their capacity to change over a higherpower and higher qualityvoltage, limit dv/dton switches and burden, mitigate electromagneticinterface (LEI), create lower exchanging misfortunes and littler basic mode voltage [1-4]. Oneof themost prominent staggered inverters is fell H-connect cells staggered inverterCHB. As it is referenced[5], CHB is comprehensively utilized in mechanical regions, for example, blowers, synchronous engines, converters

and power age plants. Notwithstanding the points of interest referenced above, there are a few issues identified with staggered inverters. The primary issue identified with these sorts of gadgets is a number of segments required to develop them [6-8]. Theyrequire a few disconnected DC sources just as countless switches which appear to be hard to be given and controlled. Considering the way thateach switch requires adriver circuit and a security circuit alongside it, utilizing countless switches ina staggered structure canmake it costly, cumbersome, and muddled. The issue

A Peer Revieved Open Access International Journal

www.ijiemr.org

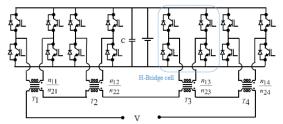

ofrequiring a few DCsources in a staggered inverter canbe tended to by utilizing transformerbased staggered inverters [9-12]. As appeared in Fig.1, these sorts of staggered invertersare incorporated with a few H-connect cells. Every cell is associated with the essential twisting ofalow recurrence transformer and the optional windingsof transformers are associated in arrangement. Inthese kinds of inverters, whichare alluded to as Cascaded TransformerMultilevelInverters, the entire power expected to supplyan electrical burden is given utilizing just a single DCunit. The utilized transformers inCTMIs offer some momentous points of interest. For example, these transformers give galvanic segregation among burden and DCsource, they diminish spillage current in PVapplication, and by ideals of appropriate transformer proportion itis conceivable to change over the voltage from an offered levelto an ideal level. Despite what might be expected, transformers in these inverters cause them to be massive and costly. Taking into account that typically aline transformer is required in certain applications, for example, adaptable **ACtransmission** frameworks (FACTS), PV boards, windturbine, and dynamicvoltage restorer (DVR), utilizing CTMIs inthese sorts of uses wouldbe exceptionally worthwhile. While, used transformers in CTMIscan take duties of the referenced line transformer. Subsequently, utilizing transformers in CTMIsinverter is legitimate when these inverters take job in the referenced applications. A few topology havebeen proposed for transformerbased staggered invertersIn[12] a typical arm CTMI has been presented. Thistopology utilizes halfconnect cells rather than full-connect cells, andit incorporates a typical arm that is integrated withtwo switches and given

ways to allthe utilized transformers. Despite the fact that this topology achieves critical segments decrease. its fundamental downside isthat the switches put atthe normal arm need to endure alot of current. The most upsetting disadvantage ofthe proposed topology in [13] isthat the present ratingof the switches increments accordance with expanding ofthe yield voltagesteps. The topology proposedin[14] endeavors to diminish theswitches consider well. by utilizing some half-lady of the hour cells rather than full-connect cells, has deservedly decreased the required parts checks. Interim, this topology utilizes a full scaffold cell whichis associated with the optional windings of the transformers. In spite of the fact that this cell contributes in expanding the acknowledged voltagelevels, it causes the deadly bad mark of losingthe galvanic separation highlight topology. [16] Has proposed utilizing threestage transformers instated of single-stage transformers in three-stage CTMIs. In this reference the creators haveworked out the outcome thatshows utilizing three-stage rather transformers than singlephase transformers can decrease the size of these sorts of staggered invertersin three-stage applications. This work led to three-stage utilizations of the traditional topology, be that as it may, the outcomes could be stretched out to different topologies too. CTMI has a significant capacity encouraging the association of photovoltaic framework to the network. For instance, the recommended topologyin this reference a half extension cell is added to the customary topology. The additional phone realizes an upgrade in he nature of the created voltage waveform. Interim, it lessens twoswitches. There canbe discovered some different works identified with this idea in [18-19].Motivated bythe talked about works

A Peer Revieved Open Access International Journal

www.ijiemr.org

over, the present article presents a decreased segments 9-levelsingle-stage topology for CTMI. Contrasted with the customary CTMI, theproposed topology utilizes a halfnumber of changes to build up a 9level staircase voltage. Being founded on CTMI, it utilizes just a single DC-source and twoH-Bridges cells. In this manner, weneed only eight changes to develop it. As such, it comprises offour switch legs, where every leg comprises of in every leg, the essential windings of transformers are associated. Moreover, we have exploited example based current control system to interface the propose topology to the framework. To this have utilized the spillage inductances of the channel. This paper is masterminded as pursue: in the following area the fundamental structure of CTMI is displayed. In area III, the proposed topology alongside its activity rule is represented. In segment IV the power misfortunes and dropped voltage of the recommended topology are researched. In area V the proposed topology is contrasted and the topology andthe traditional topologies recommended in [14]&[15]. So as to check the exhibition of the recommended topology some PC help recreations performedunder Matlab/Simulink condition. The got outcomes are appeared in area VI. In this area, two situations are considered. Atthe primary situation theinverter bears the obligation providing a neighborhood load, and in the subsequent situation, itis dependable to convey intensity of aDC unit to an AC lattice. Moreover, inthis segment, intwo distinct subsections, boththe technique of test based currentcontrol, which is intended forthe proposed topology, andthe approach of adjusting voltages ofthe capacitors are delineated. Also, demonstrate the attainability of the proposed topology, a lab manufactured model hasbeen utilized to

separate the test results. The consequences ofthe exploratory tests are given in area VII. At long last, the general workis finished up in area VIII.

# 2. CONVENTIONAL CASCADED RANSFORMERS MULTILEVEL INVERTER.

For simplicity of reference a nine-level topology of the customary CTMIis appeared inFig.1. As indicated by this figure, the essential moduleof CTMIis a H-connect cell whichis associated with a low recurrence transformer. The transformer proportion of fell transformer canbe each picked discretionarily to satisfy an ideal voltage size atthe yield side. There arethree fundamental techniques discover thetransformer proportion ofthe transformers. Inthe main methodology all the used transformers havean indistinguishable transformer proportion. Thetopology developing structure system is alluded to as symmetric topology. Inthe second and the third techniques the transformer proportions of the transformers are, individually, found out as double and ternary. Thetopologies rising up out of the second andthethird methodologies are both alluded toas awry topologies. Looking at containing an equivalent number of parts, the structure which has transformers with indistinguishable transformer proportion would build up a voltage waveform with less number of steps. Actually, astructure whichhas transformers withternary transformer proportion would build up avoltage waveform withhigher advances. Despite the fact that, nature of the created voltage can be expanded by utilizing hilter kilter techniques, it can fall apart different ofCTMI. For example, parameters lopsided CTMIwould require utilizing parts of highercurrent ratingand exchanging capacity just certain transformers of various

A Peer Revieved Open Access International Journal

www.ijiemr.org

power evaluations [18]. In the mean time, it can build the power misfortunes of the converter.

Fig. 1. Nine-level configuration of the conventional CTMI.

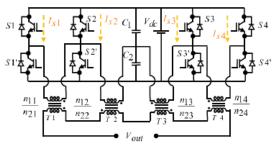

#### 3. PROPOSED TOPOLOGY

The office of utilizing just a single DC source, rather than a few disconnected ones, in fell transformers staggered inverters would reachtoa basic structureof staggered inverters. Since, thereisno requirement for thesources tobe detached, they canbe associated in arrangement or parallelto shape a unified source. Thisisa helpful component in light of the fact that, other than getting a basic source course of action, inverter would require a basic controlling framework. Then again, utilizing less numberofswitches would reach to an structure staggered inverter. ideal staggered inverterwith a solitary DCsource and less number of switches and door drivers straightforward requires controlling framework with abase number of controlling segments. Therefore, the decrease of parts inthese sorts ofconverters would build a very much setandhigh solid gadget with enhanced sizeandcost. The recommended topologycan split the quantity ofswitches and door driverswhich are required to build a nine-level fell transformers staggered inverter. Having been founded on fell transformers staggered inverter, proposedtopology utilizes just a single DCsource to change over the entire power required tosupply a neighborhood burden or network. The DCsource canbe alot of arrangement orparallel associated batteries, PVboards, energy components and so forth. The proposed topologyhas been appeared inFig.2 andthe related exchanging example is organized in table 1. As per Fig.2the recommended topology comprises offour legs and every leg containstwo unidirectional switches. Two arms of every transformerare associated with two unique legswhich are neighboring one another. It merits referencing thattwo contiguous transformers must athwart twisting on the optional side. The present appraisals ofthe switches are expressed in condition (1). As per this condition, the switches in the center legs give a present way to two transformers. In this manner, each switchin these legs, needs to endure multiple timeshigher current than thosein every cell ofthe customary CTMI. In any case, attributable to the way that the switches in the external legs are associated with just a single transformer propositions switches don't should beof high current rating. ThePeak Invers Voltage esteem (PIV) of against parallel diodesandForward Blocking Voltage (FBV) of switches in a staggered inverterare vital, which are important tobe surveyed. PIVandFBV of traditional topologies, are the equivalent. As attested in (2) PIV and FBV of the utilized equivalent to the info DC voltage esteem.

Table 1 switching strategy of suggested topology

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                    | levels |       | Switch | es statu   | is       | 4                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|------------|----------|------------------------------------------------------------------------------------------------------------------------------------|

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                    | levels | $s_1$ | $s_2$  | $s_3$      | $s_4$    | $v_{out} = \sum_{i=1}^{\infty} v_i$                                                                                                |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                    | 4      | 0     | 1      | 0          | 1        | $(\frac{n_{21}}{n_{11}} + \frac{n_{24}}{n_{14}}\mathcal{Y}_{dc} + (\frac{n_{22}}{n_{12}} + \frac{n_{23}}{n_{13}})\frac{V_{dc}}{2}$ |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                    | ,      | 1     | 1      | 0          | 1        | $\left(\frac{n_{22}}{n_{12}} + \frac{n_{23}}{n_{13}}\right) \frac{V_{dc}}{2} + \frac{n_{24}}{n_{14}} V_{dc}$                       |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                    | -      | 0     | 1      | 0          | 0        | $(\frac{n_{22}}{n_{12}} + \frac{n_{23}}{n_{13}})^{\frac{V_{obs}}{2}} + \frac{n_{21}}{n_{11}}V_{obs}$                               |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                    | 2      | 1     | 1      | 0          | -        | 112 113 -                                                                                                                          |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                    | 1      | 0     | 0      | 0          | 1        | $\left(-\frac{n_{22}}{n_{12}} + \frac{n_{23}}{n_{13}}\right)^{\frac{V_{do}}{2}} + \frac{n_{21}}{n_{11}}V_{do}$                     |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                    |        | "     |        |            |          |                                                                                                                                    |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                    |        | 1     | 0      |            | 1        | 0                                                                                                                                  |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                    |        | 1     | 1      | 1          | 1        | 0                                                                                                                                  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                     |        | 0     | 0      | 0          | 0        | 0                                                                                                                                  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                     |        | 0     | 1      | 1          | 0        | 0                                                                                                                                  |

| -2 0 0 1 1 $-\frac{n_{22}}{n_{12}} + \frac{n_{21}}{n_{13}} \frac{V_{ss}}{2}$<br>1 0 1 1 $-\frac{n_{22}}{n_{12}} + \frac{n_{21}}{n_{13}} \frac{V_{ss}}{2} - \frac{n_{21}}{n_{11}} \frac{V_{ss}}{2}$<br>-3 | -1     | 1     | 0      | 0          | 0        | $\left(-\frac{n_{22}}{n_{12}} + \frac{n_{23}}{n_{13}}\right)^{\frac{V_{dc}}{2}} - \frac{n_{21}}{n_{11}}V_{dc}$                     |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                     |        | 1     | 1      | 1          | 0        | $(\frac{n_{22}}{n_{12}} - \frac{n_{23}}{n_{13}}) \frac{V_{do}}{2} - \frac{n_{24}}{n_{14}} V_{do}$                                  |

| -3                                                                                                                                                                                                       | -2     | 0     | 0      | 1          | 1        | $-(\frac{n_{22}}{n_{12}} + \frac{n_{23}}{n_{13}})\frac{V_{de}}{2}$                                                                 |

|                                                                                                                                                                                                          | -3     | 1     | 0      | 1          | 1        | $-\left(\frac{n_{22}}{n_{12}} + \frac{n_{23}}{n_{13}}\right)\frac{V_{dc}}{2} - \frac{n_{21}}{n_{11}}V_{dc}$                        |

|                                                                                                                                                                                                          |        | 0     | 0      | 1          | 0        | $-(\frac{n_{22}}{n_{12}} + \frac{n_{23}}{n_{13}})\frac{V_{de}}{2} - \frac{n_{24}}{n_{14}}V_{de}$                                   |

| $-4 \qquad 1 \qquad 0 \qquad 1 \qquad 0 \qquad -(\frac{n_{21}}{n_{11}} + \frac{n_{24}}{n_{14}} \mathcal{V}_{dc} - (\frac{n_{22}}{n_{12}} + \frac{n_{23}}{n_{13}})^{\frac{V}{dc}} \frac{dc}{2}$           | -4     | 1     |        |            |          |                                                                                                                                    |

| \$1'=!\$1, \$2'=!\$2, \$3'= !\$3, \$4'=!\$4                                                                                                                                                              |        |       | 513    | =!\$1, \$2 | =!52, 53 | r= IS3, S4'=IS4                                                                                                                    |

A Peer Revieved Open Access International Journal

www.ijiemr.org

$$\begin{cases} I_{S1} = (\frac{n_{21}}{n_{11}}) S_1 I_{Load} \\ I_{S2} = (\frac{n_{21}}{n_{11}} + \frac{n_{22}}{n_{12}}) S_2 I_{Load} \\ I_{S3} = (\frac{n_{23}}{n_{13}} + \frac{n_{24}}{n_{14}}) S_3 I_{Load} \\ I_{S4} = (\frac{n_{24}}{n_{14}}) S_4 I_{Load} \\ S1, S2, S3, S4 \in \{0,1\} \end{cases}$$

$$\begin{cases} FBV = V_{dc} \\ PIV = V_{dc} \end{cases} \tag{2}$$

Fig. 2. Proposed topology

## 4. Investigation of powerlosses, drop ped voltage

Inthis segment, the power misfortunes and topologyare researched. The voltagedrop in an aninverter can show up an outcome of two principle issues. Here principal issue is the current of certain impedances that show up the present way, and the subsequent issue is the current of an on-state turn around voltage that shows up when proposed topology are appeared in (3) and (4) separately [20]:

$$\begin{cases} v_d + r_d^i(i) & 0 < \infty t < \varphi \\ v_{os} + r_t^i(i) & \varphi < \infty t < \pi \end{cases}$$

(3)

$$\Delta v = \sum_{i=1}^{4} (k_j^{-2} z_{t1_j} + z_{t2_j}) i_{load} + \sum_{i=1}^{4} v_{sd_j} k_j^{-1}$$

(4)

The power misfortunes identified with semiconductorswitches can be partitioned intotwo classifications. The first isthe power misfortune whichisan outgrowth of the resistive impedance and anonstate voltage which shows up alongthe way of the current. Thispower misfortune is alluded conductive influence misfortune. Condition (5) depicts conductivepower misfortune by large and condition (6) presents conductive influence lossofthe proposed topology. The second is the power misfortune that stems from the exchanging influence activity ofswitches in an electronicbased gadget. This power misfortune isknownas exchanging influence misfortune. Condition (7) recommends the exchanging powerloss of theproposed topology. It is all around recognized that every one of the parts in a powerelectronic gadget can realize a power misfortune. As per thisreality, different segments of the proposed topology, for example, non-perfect transformerscan likewise cause some power misfortunes. The power misfortunes which apear because of the nearness ofthe transformers are exhibited in (8). The complete power misfortunedetermined by(9).

$$\Delta P_{z} = \frac{1}{\pi} \left[ \int_{0}^{\theta} \left( v_{zd}(t)i(t) + r_{d}i(t)^{2} \right) dt + \int_{0}^{\pi} \left( v_{oz}(t)i(t) + r_{zw}i(t)^{2} \right) dt \right]$$

(5)

$$\Delta P_{ct} = \sum_{i=1}^{8} \Delta P_{s_i}$$

(6)

$$\Delta P_{f} = v_{dc} f_{JW} \sum_{i=1}^{8} ((t_{Qff} + t_{on})I_{s_{f}} + C_{oss})$$

(7)

$$\Delta P_{tr} = i \frac{2}{L_{out}} \sum_{j=1}^{4} (k_j^{-2} r_{i_1 j} + r_{i_2 j})$$

(8)

$$\Delta P_t = \Delta P_{ct} + \Delta P_f + \Delta P_{tr}$$

(9)

#### 5. COMPARISON

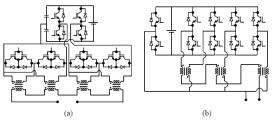

Two new topologies interm of CTMI have been proposedin[14][15]. For simplicity of reference twosymmetric nine-level designs for thesetwo topologies are appeared inFig.3 and (b). The topologyin[14], by goodness of two capacitors, separates the voltage of the DC-source considerably. Throughthis way it gives a square ACvoltage to be utilized as the info voltage ofthe transformers. As per Fig. 3 (a) thetopology proposedin[14]

A Peer Revieved Open Access International Journal

www.ijiemr.org

diminishes the segments tally regard tothe ordinary topology. Despite the fact that the topology recommended in[15]has deservedly diminished the quantity of switches, ithas lost themost significant element of giving galvanic disengagement. Table 2 organizes the expected segments to incorporate a nine-level arrangement ofthe proposed topology, the regular topology, andthetopologies recommended in[14]and [15]. So as to think about theelectrical highlights of thesefour topologies, three primary electrical qualities ofthem have been assessed. To thisend, initially, the general droppedvoltage over the semiconductorsis assessed. Besides, the conductive power misfortunes ofthe used semiconductorsare evaluated. For curtness, since previously the mentioned topologies incorporate the equivalent indistinguishable transformers, evaluating the power misfortunes and the dropped voltage emerged from them are stayed away from. Thirdly, the exchanging power misfortunes are considered. The conditions misfortune identified with the proposed topology are, separately, refered to in conditions 4and9. These conditions for the traditional topology and the topologies of [14] and [15] can be gotten by following the present ways inthese topologies. Table 3 records theswitches qualities that considered to separate examination results. Every one of theswitches utilized, are viewed as industrially accessible and every one of the information recorded, are separated from theirdatasheets. Since switches situated atthe two center legs of the proposedtopology need to endure multiple times highercurrent than those situated atthe two external legs, unique kinds of switches for theproposed considered topology. Thesetwo sorts vary in current appraisals. This additionally is the situation for switches

used in topologiesof[14][15]. So as exactly dothe examination, five current estimations of 2 (A), 4 (A), 6(A), 8(A), and 10(A) are thought tobe given bythe thought about topologiesFig.4(a) demonstrates the general droppedvoltage four thought about topologies. As indicated by these figures the proposedtopology offers the least dropped voltage. Thisis additionally the situation when looking at the conductive power misfortunes of these four topologies as appeared in Fig. 4 (b). As to exchanging misfortune, since power the four unidirectional switches in [14] work at the recurrence of the yield voltage (50Hz), this topology has the most reduced exchanging influence misfortune among the topologies under correlation as displayed in Fig 4. (c). despite what might be expected, though every one of the switches in the regular topologies worked at the discovered exchanging recurrence this topology has the astounding exchanging most misfortune. **Inthis** term theproposed topology comes seconds and thetopology in the info DCvoltage is thought tobe 200v and the exchanging recurrence is viewed as 5 KHz.

**Table 2. Comparison**

| 41           | Numbers Numbers of |                | Numbers Transformers  | FBV & PIV     |  |

|--------------|--------------------|----------------|-----------------------|---------------|--|

| topologies   | of switches        | switch drivers | of equal power rating | g of switches |  |

| conventional | 16                 | 16             | 4                     | Vdc           |  |

| [14]         | 12                 | 8              | 4                     | Vdc           |  |

| [15]         | 10                 | 10             | 3                     | Vdc           |  |

| The proposed | 8                  | 8              | 4                     | Vdc           |  |

Table 3. characteristics of the considered switches

| Switch type | Ros   | Vos | Drain-source voltage | Current rating | Tum-on time | Turn-off time | Coss |

|-------------|-------|-----|----------------------|----------------|-------------|---------------|------|

|             | (Ω)   | (v) | (V)                  | (A)            | (ns)        | (ns)          | (pF) |

| IRFP250     | 0.073 | 1.6 | 200                  | 33             | 25          | 60            | 420  |

| STP10NB20   | 0.25  | 1.5 | 200                  | 10             | 15          | 8             | 135  |

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 3. (a) Proposedtopologyin[14]. (b) Proposedtopologyin[15]

Fig 4. (a) Total droppedvoltage overthe semiconductors. (b). Completeconductive powerloss of thesemiconductors. (c) Total exchanging powermisfortunes of the semiconductors.

#### 6. SIMULATION RESULTS

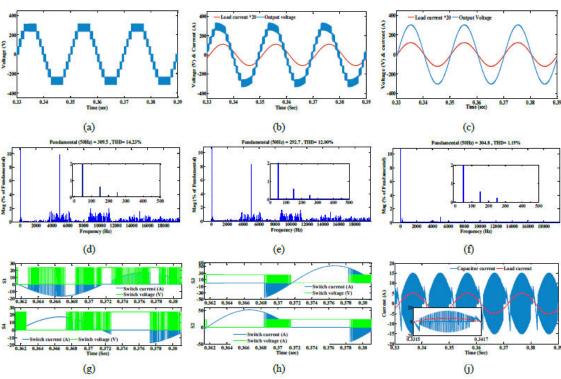

Inthis area the presentation of the proposed topology has been examined througha model reenacted under mathlab/Simulink The determinations condition. ofthe mimicked model are appeared intable 4. The reproduced nine-level staggered inverter modelis considered tosupply a RL heap of  $(50\omega + 75\text{mh})$ 0.9 powerfactor with ostensible voltage and recurrence of 220v 50Hz, individually. and Fig 5 (a) demonstrates the yield voltageofthe topology recommended inno condition. Fig 5 (b) demonstrates the yield voltage and burden current whenitsupplies the referenced RLload. Moreover, the exhibition of the proposed topology within the sight of an unadulterated resistive heap of  $50\omega$  is appeared in Fig. 5 (c). Investigating these three figures itisseen that the high-recurrence music evaporate as the powerfactor of the heap expands, this marvel is outlined by alluding to Fig. 6. As appeared in this figure, every transformer contains two spillage inductances inits essential and auxiliary sides. The essential inductance can moved the auxiliary side, to demonstrated general spillage as

inductance at the optional side. Sincethe auxiliary sidesof the transformers associated in arrangement, their spillage inductancescan be displayed as a unified inductancewhich is associated with the heap arrangement. As appeared in Fig. 6 (c) and as per (10) the high-recurrence parts ofthe voltage influence the spillage impedance to be definitely high (2 □nfLst □□ Rload). Thus, asthe heap powerfactor builds thehigh-recurrence parts of voltage vanish at the yield. Despite what might be expected, as the inductive normal for the heap expands (control factor diminishes), for the high-recurrence parts the inductive trademark overwhelms the resistive normal for the heap, so that, the high-recurrence segments will show up at the yield voltage.FFT investigation of the yield voltage under the three referenced stacking conditions are portrayed in Fig. 5 (d), (e), and (f). As indicated by these FFT examinations and condition (10), since under unadulterated resistive stacking condition the higher-recurrence sounds are alleviated, the inverter offers a yield voltage higher quality in this condition. Furthermore, as per these figures the prevailing sounds show up around exchanging recurrence (the exchanging recurrence is viewed 5 KHz) Additionally, so as to expect a stacking condition under which the proposed inverter gives both dynamic and receptive forces, the stacking state of the previously mentioned resistive-inductive burdens is thought about. The flows of the switches in the two external legs and those of the switches in the two center legs are, separately, appeared in Fig. 5 (g) and (h). Eating times, these figures show the FBV estimations of the switches and PIV estimations of the counter parallel diodes. As expressed before and delineated by (1) the switches in the center

A Peer Revieved Open Access International Journal

www.ijiemr.org

legs endure multiple times higher current regard to those in the external legs. Notwithstanding, as prosecuted in (2), on account of FBV and PIV, every one of the switches and hostile to parallel diodes withstand a similar voltage which is equivalent the info DC-voltage esteem. So as to manage responsive power and to give way to the switch current a capacitor is associated in parallel to the DCsource in the

ordinary CTMI as appeared in Fig. 1. The two capacitors in the proposed topology (C1 and C2 in Fig. 2) can bear a similar assignment. The heap current alongside the capacitor current, under the referenced resistive-inductive stacking condition (providing dynamic and receptive power), are appeared in Fig. 5 (j)

Table 4. Specifications of the simulated model

| Transformers                           | Wi      | inding 1 paran | neters            | Winding 2 parameters |         |        | Magnetization resistance and inductance |             |

|----------------------------------------|---------|----------------|-------------------|----------------------|---------|--------|-----------------------------------------|-------------|

| Transformers .                         | V1(rms) | R1(mΩ)         | L1(mH)            | V2(rms)              | R2(mΩ)  | L2(mH) | Rm(Ω)                                   | Lm(H)       |

| T1,T4                                  | 24      | 2.304          | 0.293             | 78                   | 24.336  | 3.1    | 576                                     | 1.8335      |

| T2,T3                                  | 12      | 0.576          | 0.073             | 78                   | 24.336  | 3.1    | 144                                     | 0.45837     |

| $C1,C2 = 2200 \mu\text{F}$ $Vdc = 24V$ |         |                |                   |                      |         |        |                                         |             |

|                                        |         |                |                   |                      | 9.7 997 |        |                                         | 200 200 200 |

|                                        |         | 1 3            | —Load current *20 | -Output voltage      | ''      | 400-   | — Load current *20 — Output Voltag      | *           |

Fig. 5. Recreation consequences of the yield voltage, load current, FFT investigations, and switches voltages and flows. (an) Output voltage in no heap condition, (b) yield voltage and burden current when providing the RL load (c) yield voltage and burden current when providing the unadulterated resistive burden. (d) FFT investigation of the yield voltage in no heap

condition. (e) FFT examination of the yield voltage when providing the RL load. (f) FFT examination of the yield voltage when providing the unadulterated resistive burden. (g) Voltages and flows of the switches of the two external legs. (h) Voltages and flows of the switches of the two center legs. (j) Load and capacitor flows

A Peer Revieved Open Access International Journal

www.ijiemr.org

when giving dynamic and receptive power (resistive-inductive stacking condition).

Fig 6. (a) Typical transformer model. (b) Simplified transformer model. (c) Simplified model of the transformers in the proposed topology.

$$V_{out}(n) = \frac{\sqrt{R_{load}^2 + (2\pi n f L_{load})^2}}{\sqrt{R_{load}^2 + ((L_{load} + L_{s_t})(2\pi n f))^2}} \left( \sum_{j=1}^4 k_j a_{n_j} \sin(n \omega t) \right)$$

(10)

#### A.Sample based current control strategy

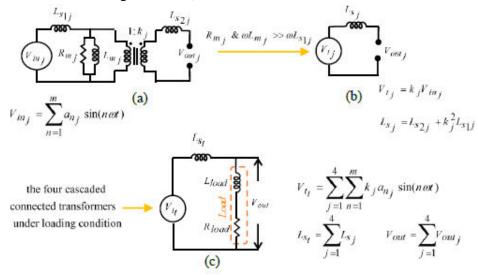

As we probably am aware, staggered inverters are assuming a noteworthy job in sustainable power source assets frameworks and smaller scale matrix applications. Where, they convey the power created by inexhaustible assets to the framework [22-24]. Since, transformers are predominately used to associate staggered inverters to the matrix, a transformer-based inverter can be an appropriate option in these sorts of utilizations. Moreover, the spillage inductances of the transformers can be utilized as a present channel [25]. In this manner, the requirement for an additional channel can be killed. Another advantage of utilizing transformers is that they can give a galvanic detachment [2627]. The present area examines the presentation of lattice tied model of the recommended topology. The Specifications of the model and lattice are appeared in table 5 and the plan of such a framework is delineated in Fig. 7 (a). The technique of test based current control has been received to convey a given measure of dynamic capacity to the lattice through the proposed staggered inverter. The dynamic power is thought to be a shifting force from 15kw to 25kw. In the interim, the spillage inductance of the transformers have been utilized as a present channel. The situation of matrix voltage regard to the levels is delineated in Fig. 7 (b). As per this figure at each example of the time the brace voltage is encompassed by two potential degrees of the inverter yield voltage. One of the encompassing level is in the upper position (upper level), and the other one is in the

A Peer Revieved Open Access International Journal

www.ijiemr.org

lower position (lower level). These two levels are utilized to get the infused current pursue the reference current. To this end, toward the part of the arrangement time frame, the infused current is contrasted and the reference current. On condition that the infused current worth is higher than that of the reference current the exchanging example of the lower level will be executed at the following exchanging period, or the consequences will be severe, the exchanging example of the upper level ought to be executed. For example, as appeared in Fig. 7 (b), during time interim from 0.007 to 0.008 second the framework voltage encompassed by two levels (level 3 and level 2), where, level 3 is the upper level and level 2 is the lower level. In this way, during the referenced time interim, if in a specific exchanging period the deliberate current surpasses the reference current, the exchanging example identified with level 2 (lower level) will be executed at the following exchanging period. This will destroy down the infused current to keep it some place close to the reference current. In actuality, on condition that the deliberate current is lower than the reference current, the exchanging example identified with level 3 (upper level) will be utilized at the following exchanging period. This will ascend the infused current to get up to speed

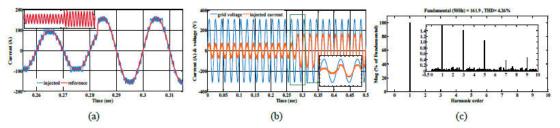

with the reference current. Accepting that the power misfortunes are immaterial, the reference current can be gotten from (11) Fig. (a) demonstrates [28]. 7 methodology of acquiring the reference current. As appeared, the controlling framework needs a PLL to decide the recurrence of the matrix. K1 and K2, are gains that are utilized to downsize the framework and DC voltages so as to make them good with the sign preparing unit. The reference dynamic power and the reference responsive power can be determined by embracing hang control approaches in small scale network applications [23-31] or different strategies for most extreme power point following (MPPT) in PV or wind turbine applications and so on [32-35]. Fig. 8 (a) demonstrates both the reference current and the infused current to the matrix which is a reproduction consequence of the reenacted model. So as to have solidarity power factor, on account of edge the infused current ought to fluctuate in accordance with the network voltage. This issue is delineated in Fig. 8(b). At last the FFT investigation of the infused current is appeared in Fig. 8 (c).

$$i^{ref}(t) = I_m^{ref} \sin(\omega t + \alpha) = \frac{2P_{ref}}{V^{grid}} \sin(\omega t) - \frac{2Q_{ref}}{V^{grid}} \cos(\omega t)$$

(11)

Fig. 7. (a) Grid tied model. (b) matrix voltage and encompassing levels

Vol 08 Issue09, Sept 2019

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig.8. Reproduction consequences of lattice tied model. (a) Reference current and infused current. (b) Injected current and network voltage. (c) FFT investigation of the infused current

Table 5. specifications of grid-tied model

| transformers      | W                                                            | inding 1 para | meters                   | W       | inding 2 paran   | neters | Magnetization resistance and inductance |        |

|-------------------|--------------------------------------------------------------|---------------|--------------------------|---------|------------------|--------|-----------------------------------------|--------|

| transformers      | V1(ms)                                                       | R1(Ω)         | L1(mH)                   | V2(rms) | R2(mΩ)           | L2(mH) | $Rm(\Omega)$                            | Lm(H)  |

| T1,T4             | 750                                                          | 0.1125        | 2.69                     | 83      | 1.38             | 0.0329 | 28125                                   | 89.525 |

| T2,T3             | 375                                                          | 0.028         | 0.67                     | 83      | 1.38             | 0.0329 | 7031.3                                  | 22.381 |

| $L_{f}(H)$        | 2*(0.00269*9*2+3.289*10*3)+2(0.028*(4.5)*2+3.289*10*3)=0.003 |               |                          |         |                  |        |                                         |        |

| $C_1 = C_2 = 470$ | $C_1 = C_2 = 4700 \mu F$ $V_{dc} = 750 \text{ V}$            |               | C <sub>f</sub> (F)=460µF |         | $P_{ref} = 25kw$ |        | Vt [Grid] = $220\sqrt{2}\sin(314t)$     |        |

#### **B.** Capacitors voltage balancing strategy

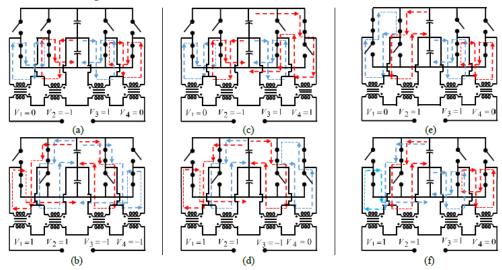

voltage of the two capacitors. Alluding to table 1 we understand that lone the exchanging examples identified with the switches S2, S'2, S3, and S'3 influence the mid-point voltage, though they give current ways which experience the capacitors, while switches S1,S'1, S4, and S'4 give current ways which go, straightforwardly, through the DC-source. Likewise experiencing this table we recognize that the exchanging examples identified with the degrees of 2, -2, 3, - 3, 4, and - 4 cause an equivalent current to be move through the capacitors. Subsequently they have no impact on the showed up irregularity voltage in the midpoint. Despite what might be expected, in the exchanging examples identified with levels 0, 1, and - 1 at each occurrence of the exchanging time frame just one of the two capacitors is capable to give the present ways. This prompts a disparity of voltage over the capacitors. As appeared in table 1 there are two conceivable exchanging designs for every degree of 1 and - 1, additionally four potential examples for level zero. The referenced methodologies are delineated in Fig. 9 with fastidious subtleties. So as to, quickly, demonstrate the present ways which influence voltage equalization of the two capacitors, just the two appropriate examples for level zero and level 1 together with exchanging examples of levels 2 and 3 are portrayed in these figures. The exchanging examples of different levels and related current ways could be anticipated by alluding to table 1. As indicated by Fig. 9, in the four demonstrated examples for levels zero and 1 just one of the two capacitors bears the obligation of giving current ways which experience switches S2, S3 or S'2 and S'3. This would prompt an imbalance of voltage over the capacitors. Likewise as indicated by this figure in levels 2 and 3 the two capacitors similarly give current ways. So it bodes well that the voltages of the capacitors stay equivalent in these levels. This is, additionally, the situation in levels -2,- 3, - 4, and 4 (not appeared). So as to

A Peer Revieved Open Access International Journal

www.ijiemr.org

have the two capacitors get an equivalent voltage, the two conceivable exchanging examples ought to be executed in a progressive exchanging period when acknowledging levels 1 and - 1. Additionally two changing examples out of the four potential examples can be received to acknowledge zero level and equivalent voltages over the capacitors. It is to be

referenced that the two chose designs for zero level must contrast in the conditions of switches S2, S'2, S3, and S'3. Despite what might be expected, the conditions of switches S1, S'1, S4, and S'4 are insignificant in the chosen examples. Anyway so as to have a lower exchanging recurrence it is attractive to have steady states for these switches.

Fig. 9.switching examples and current ways. (an) and (b) the two legitimate examples and current ways to acknowledge level zero. (c) and (d) the two examples to acknowledge level one. (e) and (f) exchanging examples of level two and level three.

#### 7. Experimental result

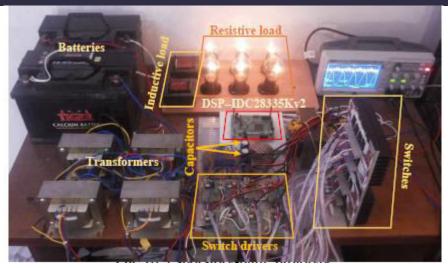

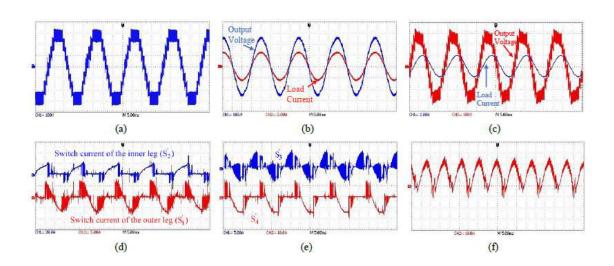

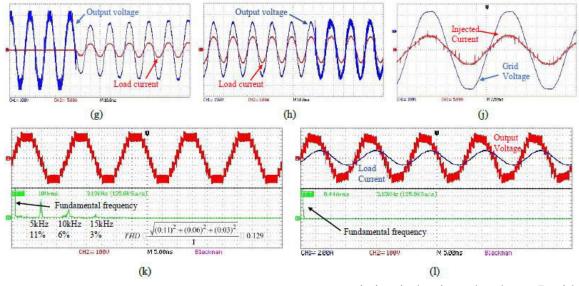

So as to demonstrate the practicality of the proposed topology, a research center fabricated model has been utilized. Fig. 10 demonstrates a photograph of the utilized model and table 6 records the particulars of the model in various modes. DSP-IDC28335Kv2 has been received to process the sign of the switches entryways drivers and two arrangement associated batteries of 12v and 60Ah are utilized as the DC-voltage providing unit. The model has gone under various tests. Right off the bat, its yield voltage has been acquired under no heap condition. Fig. 11(a) demonstrates the ninelevel staircase yield voltage came about because of this test. It is to be noticed that, a

sinusoidal voltage with pinnacle estimation of 220 V and recurrence of 50 Hz has been expected as the ideal yield voltage. As appeared, there is about 10v dropped voltage in no heap condition that emerges from the presence of the on-state turn around voltages of the switches. Also, the model has been inspected when it supplies an unadulterated resistive heap of 400w, the outcome is appeared in Fig. 11 (b). As delineated in the recreation segment and represented by (10), when providing an burden unadulterated resistive the recommended offers inverter progressively sinusoidal yield voltage. Moreover, the model execution has been

A Peer Revieved Open Access International Journal

www.ijiemr.org

examined when it is stacked by a resistiveinductive heap of 250w with slack power factor of 0.8. The outcome has been appeared in Fig. 11 (c). Besides so as to research the impact of the heap momentum on the switches the ebb and flow of the four lower switches under the referenced stacking condition are appeared in Fig. 11 (d) and (e). The info current for this heap is likewise appeared in Fig. 11 (f). As referenced in the reenactment part, as indicated by Fig. 11 (d) and (e) the switches situated in the two inward legs endure multiple times higher current than those in the external legs. So as to give greater dynamic clearness. conduct recommended topology is additionally tried. Fig. 11(g) demonstrates conduct of the model inverter when it reactions to a heap change from no heap to an unadulterated resistive heap of 400w. In the interim Fig. 11(h) portrays the reaction to the condition under which the heap changes from 150w unadulterated resistive burden to a resistiveinductive heap of 150w with a slack power factor of 0.9. The other significant trial test that the model passed effectively, was the test that practiced under brace tie condition. In this test, by receiving test based current procedure, the proposed structure bore the duty of conveying 800w dynamic capacity to the lattice. The consequence of this test is exhibited in Fig. 11 (j). As appeared, the voltage of the vast matrix is 220 2sin100 □ t. In this test the voltage extent of DC-source

was changed in accordance with be 80v. As demonstrated the infused current, account of stage, is in accordance with the network voltage. This demonstrates the topology has an proposed presentation in this term. Test FFT investigation of the yield voltage and burden current are, separately, given in Fig. 11 (k) and (1). As appeared in Fig. 5 (d) and (e) in the reenactment part, the low recurrence music estimations of the yield voltage are unimportant and the most discernible music are of higher recurrence which rise around numerous of the exchanging recurrence. Since exchanging recurrence is a long way from the crucial recurrence these sounds can without much of a stretch be killed by some little channels. The test result delineated in Fig. 11 (k) loans confidence to the FFT examination acquired in the reenactment part. Separating the symphonious qualities from Fig. 11 (k) THD estimations of the yield voltage is determined to be 12.9%. As to FFT examination of the heap current, since the spillage inductances of the transformers and the inductive component of the heap go about as current channels, the heap current has a mutilation free sinusoidal waveform. Henceforth, as appeared in Fig. (1), no huge symphonious rises in the FFT investigation of the heap current. In this manner THD estimation of the heap current is zero.

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig. 10. Laboratory-built prototype

Table 6. Specifications of prototype model

| Parameters                                                                                 | supplying local load           | Grid-tie mode                   |

|--------------------------------------------------------------------------------------------|--------------------------------|---------------------------------|

| Input voltages of T <sub>1</sub> & T <sub>4</sub>                                          | 24 V                           | 80 V                            |

| Input voltages of T <sub>2</sub> & T <sub>3</sub>                                          | 12 V                           | 40 V                            |

| Leakage impedance of transformers [R2 L2]                                                  | $[1.2\Omega + 0.4 \text{ mH}]$ | $[0.36\Omega + 2.8 \text{ mH}]$ |

| Magnetization resistance and inductance [Rm Lm]                                            | [1440 Ω 4.5 H]                 | [1440 Ω 4.5 H]                  |

| Transformer ratio of T $_1$ & T $_4$ ( $N_{11}/N_{21}$ & $N_{14}/N_{24}$ )                 | 0.31                           | 1                               |

| Transformer ratio of T <sub>2</sub> & T <sub>3</sub> ( $N_{12}/N_{22}$ & $N_{13}/N_{23}$ ) | 0.155                          | 0.5                             |

| Switching frequency                                                                        | 5 kHz                          | 35 kHz                          |

| C <sub>1</sub> & C <sub>2</sub>                                                            | 4600 μF                        | 4600 μF                         |

A Peer Revieved Open Access International Journal

www.ijiemr.org

Fig 11. Exploratory outcomes. (a) yield voltage in no heap condition. (b) load current and yield voltage when providing the unadulterated resistive burden. (c) load current and yield voltage when providing the resistive-inductive burden. (d) and (e) switches current. (f) Input current. (g) reaction from no dynamic heap unadulterated resistive burden. (h) dynamic reaction from unadulterated resistive burden to inductive-resistive burden. (j) infused current and the framework voltage when inverter infuses current to the lattice. (k), and (1) FFT investigation of the yield voltage and burden current individually.

#### 8. CONCLUSION

Thispaper set forth anovel nine-level topology fortransformer based staggered inverters. Theproposed topology deservedly lessen switches tally of aninelevel single-stage staggered inverter. To demonstrate the possibility ofthe proposed topology, by utilizing amodel reenacted underMathlab/Simulink condition research center constructed model, it went under two distinct tests. Right off the bat, its exhibition was surveyed when providing a neighborhood load. The heap was thought to beeither an unadulterated resistive burden ora resistive-inductive burden. Besides, utilizing based control current technique, its exhibition was reviewed under matrix tiedcondition. By utilizing reproduced modelinthe last test, theproposed topology assumed the liability of conveying an expected dynamic intensity of 15kW, and 25kW tothe matrix. In the exploratory testthepower worth infused to the lattice viewed as 800w. Since the CTMIs for the most part utilize just a single DCsource theyare an equipped competitor in microgridand PV application. Being founded onCTMIs, theproposed topology utilizes less quantities of parts and offers indistinguishable preferences from customary topologydoes. When receiving example currentcontrol the based methodology in gridtie applicationsan inductive component is required to be betweentheconverter and network. In thispaper the spillage utilized as the inductivechannel. This encouraged executingthe example based current control technique and therefore the requirement foran additional channel is killed. The other bit of leeway of utilizing transformers wastheir giving a galvanic detachment. To aggregate upthe cultivated tests checked the

A Peer Revieved Open Access International Journal

www.ijiemr.org

attainability and practicality of the recommended topology.

#### REFERENCES

- FZPeng, JWMcKeever,DJ AdamsA power line conditioner using cascade multilevel inverters for distribution systems, IEEETrans. Ind. Appl., Vol. 34, no. 6, pp. 1293 1298, nov. 1998.

- 2. LMTolbert, FZPeng,T.G. Habetler, —Multilevel converters for large electric drives. *IEEE Trans. Ind. Appl*, Vol. 35, no. 1, pp. 36-44, Aug. 1999.

- 3. JDixon, JPereda, CCastillo, S.Bosch,

—Asymmetrical multilevel inverter for traction drives using only one DC supply, IEEE Trans Veh, Techno, Vol. 59, no. 8, pp. 3736-3743, Oct. 2010.

- 4. T.Poompavai, A.Chitra, C.Srinivas, K. Giridharan, —A meticulous analysis of induction motor drive fed from a nine-level Cascade H-Bridge inverter with level shifted multi carrier PWM, I in *Proc. IEEE Int. Conf. on Smart Structures and Systems (ICSSS)*, 2013, pp 6-12.

- 5. Y.Suresh, A.K.Panda, —Research on a cascaded multilevel inverter by employing three-phase transformers, *IET Power Electron*, Vol. 5, no. 5, pp. 561 570, Jun. 2012.

- 6. Masaoud, HWPing, SMekhilef, ASTaallah, —New three-phase multilevel inverter with reduced number of power electronic components, IEEE *Trans. Power Electron.*, Vol. 29, no. 11, pp. 6018 6029, Jul. 2014.

- 7. E.SamadaeiSAGholamian,.

Sheikholeslami, J. Adabi, —An envelope type (E-Type) module: ysymmetric multilevel inverters with reduced components, IEEE Trans. Ind. Electron., vol pp, no. 99, pp. 1, Jun. 2016.

8. M.Hasan, S.Mekhilef, M.Ahmed,

—Three-phase hybrid multilevel inverter with less power electronic components using space vector modulation, *IET Power Electron*, Vol. 7, no. 5, pp. 1256 – 1265, May. 2014.