A Peer Revieved Open Access International Journal

www.ijiemr.org

### COPY RIGHT

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

2019IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

IJIEMR Transactions, online available on 4<sup>th</sup> Sept 2019. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-08&issue=ISSUE-09

Title HIGHFREQUENCY AC-POWERSUPPLYFORMULTILEVEL INVERTERS

Volume 08, Issue 09, Pages: 487–502.

Paper Authors

### B BHARGAVI, A SWAPNA, L BHAVANA

Anu Bose Institute of Technology K.S.P Road, New paloncha, Bhadradri Kothagudem, Telangana, India

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

### HIGHFREQUENCY AC-POWERSUPPLYFORMULTILEVEL INVERTERS

B BHARGAVI<sup>1</sup>, A SWAPNA<sup>2</sup>, L BHAVANA<sup>3</sup>

<sup>1,2,3</sup>UG Students, Dept. of Electrical and Electronics Engineering, Anu Bose Institute of Technology KSPRoad, Newpaloncha, BhadradriKothagudem, Telangana, India. banothubhargavi@gmail.com<sup>1</sup> angothswapna282@gmail.com<sup>2</sup>

**Abstract:** - This paper proposes traded capacitor stunned inverter forhigh repeat AC control dispersal structures. The proposed topology conveys a staircasewaveform with highernumber of yield levels using less sections stood out from a couple of existing traded capacitor amazed inverters in the composition. This topology useful where hilter kilter DCvoltagesources are open for instance if there ought to emerge an event of manageable power source estates based AC little scale frameworks and present-day electricvehicles. Utilizing the open DC sources as commitments for single inverter handles the significant issue of partner a couple of inverters in parallel. Moreover, theneed to stack voltagesources, like batteries or super-capacitors, in course of action which solicitation charge leveling estimations, are discarded as the voltage sources used offer a mutual view. The inverter intrinsically deals with the issue of capacitorvoltage modifying as each capacitor is charged to the value proportional to one of information voltage each cycle. State assessment, setbacks and the assurance of capacitance areexamined. Reenactment and preliminary outcomes at different scattering frequencies, control levels and yield consonant substance are given todemonstrate the attainability of the proposed amazed invertertopology.

**Index Terms:** -H-bridge, HFAC PowerDistribution, high frequency DC/AC Inverter, MultilevelInverter, selective harmonic elimination, and switchedcapacitor

#### I. INTRODUCTION

The great position that High Frequency Alternating Current (HFAC) PowerDistribution Systems (PDS) offerover customary Direct Current (DC) PDS isthat HFAC PDS abstains from the prerequisite fora rectifier and a channel sort out atthe front-end powersource, and the necessity foran inverter in the reason for burden power supply [1], [2]. This liberal diminishing in the amount of force change stages realizes lower fragment number, thusly improving steady quality and capability, while decreasing the cost. HFAC

PDS helps in reducing the size of standoffish parts which prompts higher power thickness structures, improves heat allocation and has idle ability to use connector-less power move. More diminutive yield capacitorsimprovedynamicresponse. Highvoltage low-current scattering without a lot of a stretch be cultivated utilizing limited HFtransformers. They moreover offer the flexibility to cook loads at different voltage levels, give galvanic partition and are essential to recognize connector-less power

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

move. Killing a tremendous significance of AC when experiencing a zero is easier than killing colossal DC. А couple of examinations exhibit that frequencies in excess of power source, a HF scattering line and motivation behind burden voltage controller modules. These systems use resonating converters to update capability, control factor and imperativeness thickness, and lessen threatening EMI impacts [3], [4]. In 1980sNASA led inspect on HFACPDS for its space station. A singlephase structure assessed at 25kWwith20kHz line repeat and 440Vrms linevoltage executed was successfully [5]. Atthis repeat, the imperativeness moved per cycleislowerbydifferent occasions when stood out from a 400 Hz structure (which in like manner fail to give profitable and strong course of action [6]). The amount of parts is reduced by a factor of 5 and influence adversity by 67% when appeared differently in relation to three-organize systems [1]. Because of the recently referenced points of interest, HFACPDS havebeen furthermore examinedin various fields. An expansive review of HFACPDS for media transmission, PC and aeronautics structures has been displayed in [7]. Papers ensure and construe thatHFAC plan grasp a couple of obstructions in beneficial power transport. This paper researches traded capacitor stunned inverters (SCMLI) as information hotspots for HFACPDS. Extension of MultilevelInverters (MLI) can be attributed to he enthusiasm for higher power kinds of apparatus in he business and the capacity of MLI to amuse industry needs with a couple of engaging characteristics [14]. With addition in number of voltagelevels, the fused yield waveform hasmore advances, which fundamentally mitigates the symphonious substance in he yield. MLI are widely orchestrated into impartial point cut, capacitor propped and fell sorts [15]. Inconsistent DC interface capacitor voltage and extended part count to get higher voltagelevels are the noteworthy disservices fordiode propped (DCI) and capacitor cut (CCI) types, however fell Hassociate CHBMLIdemand tolerably higher number of isolated DC voltagesources to get higherlevels. A couple of topologies of MLIthat don't fall into the grouping of the three recently referenced inverters have furthermore been starting late conveyed. Coupledinductor based MLI havebeen discussed in [16], [17]. The structure is clear yet isn't possible to procure higher levels. A ground-breaking topology reliant on switching voltage portion is shown in [18]. Topologies of SCMLI conveyed starting late is investigated in the accompanying section.

### II. REVIEW OF SWITCHEDCAPACITOR MULTILEVELINVERTERS

SCMLI havebeen getting thought starting late [19]-[32]. Thisnew gathering of MLI unavoidably handles theissue of unbalanced capacitorvoltages that harrows different old style topologies. It is in like manner possible to convey highernumber of voltagelevels while using a lone voltagesource not in any way like fell MLI. The fundamental designing in this gathering of MLI consolidates a front-endSC based DC-DCconverter that can coordinate different levelsatthe DC transport fell with a Haugmentation to procure the looking at the yield. Number of yield levels can be overhauled by extending the amount of data voltage sources, SC and power switches in the front-end SC DC-DCconverter. In any case, the amount of additional parts and data voltage sources required to improve the level **SCMLI** vield voltage by is extraordinarily diminished when stood out

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

from the customary topologies. SC DC-DCconverters offer the good position to information voltage change over to indispensable diverse yield levels without utilizing inductors. This voltage change is polished by charging the SCs to enter voltage degree first (by partner SC in parallel to source) and later interfacing the data voltage source and SCs in plan to the load. This direct idea can be contacted make various voltage levels. A fell MLI subject to SC voltage doubler is proposed in [21], [23]. A comparative equipment, without affiliation, is connected course with higherlevelsin [19], [20]. It relies upon the standard of midway charging of capacitors. Regardless, it is incredibly difficult to control the voltage unequivocally. Using a lone course of action parallel SC unit, a bidirectional SCMLI is presented in [31]. The typical segment in all SCMLI topologies is the back-end H-interface inverter. Thusly, the key is to design the front-end SC DC-DC converter that can make diverse levels.A few Pulse Width Modulation (PWM) strategies have been inquired about. Stage move change system for HFAC PDS was executed in [21]. The introduction of the stunned conveyor based sinusoidal PWM and SHE with staircase guideline has been surveyed in [22]. It derives that the last offers an unrivaled trade off as it mitigates the sounds to an attractive substance and avoids higher transistor trading disasters.

parallel movement of inverters are trying and solicitation pushed control figurings [32]. Thispaper, thusly, focuses to research novel SCMLI topologies with various data voltagesources, sharing a mutual conviction, that can be used in zones like microgrids and electricvehicle frameworks where uneven data sourcesare open with complement onhigh repeat AC control scattering.

# III. PROPOSED TOPOLOGY AND OPERATINGPRINCIPLE

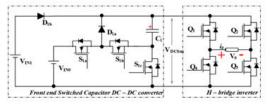

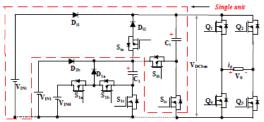

Theproposed 7-levelSCMLI, appeared in Fig.1, comprises of aSC based DC-DCconverter which utilizes two information sources(VIN0 and VIN1), three transistors (S1a, S1b, and S1c), two diodes (D1a and D1b) and a capacitor (C1). DC levels acquired attheinverter DC transport incorporate VIN0, VIN1, VIN0+VIN1. The H-connect inverter utilizing transistors Q1 to Q4 successfully creates 6bipolarlevels and azero (0, ±VIN0, ±VIN1, ±(VIN0 + VIN1)) over the heap. For essential investigation, it is expected that the switches and the voltagesources utilized are perfect, capacitance is enormous enough to keep up a consistent voltageandsupply steady yield current, andthevoltage swell crosswise over them is little enough tobe disregarded. Table I clarifies the exchanging rationale of the proposedinverter. The working states are clarified in the accompanying subsections.

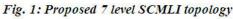

### A. Outputvoltage = $\pm V_{IN1}$ state

Capacitor C1, is charged tothe info voltage VIN1 through D1b byturning ON transistor S1c. Transistors S1a, S1b anddiode D1a stay killed. The DC transport voltage atthis state is equivalent to VIN1 as VIN0 is closed by killing transistor S1a. Voltage source VIN1 alonesupplies capacity tothe heap. Fig. 2(a) delineatesthe comparable circuitfor V0 = +VIN1.

### **B.** Outputvoltage = $\pm V_{IN0}$ state

For typical activity of the proposed inverter, VIN0 > VIN1. In the DC-DCconverter, just transistor S1a isturned VIN0 + VIN1 (d) Vo

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

= 00N while different transistors are killed. In this way, VIN0 isassociated

to the DC transport through diode D1a. As VIN0 > VIN1,diode D1b is invert one-sided and thus squares VIN1. Fig. 2(b) delineates the comparable circuit for V0 = +VIN0. The capacitor C1 isopen during this state. Hence, its voltage staysat VIN1.

Fig. 2: Equivalent circuits of the 7-level SC MLI to obtain different voltage levels.(a)  $V_o = V_{IN1}$  (b)  $V_o = V_{IN0}$  (c)  $V_o = V_{IN0} + V_{IN1}$  (d)  $V_o = 0$

### C. Output voltage = $\pm(V_{IN0} + V_{IN1})$ state

Capacitor C1, chargedto VIN1, is associated inarrangement with information voltagesource VIN0 by turning ON transistors S1a and S1b. DiodeD1b is turn aroundonesided and squares VIN1. The netvoltagethatshows up over the DC transport presently is equivalent to VIN0+ VIN1. Inthis state, input voltagesource VIN0 and capacitor C1 supplycapacity to theheap. Fig. 2(c) portrays the equal circuit for V0 = +(VIN0 + VIN1).

#### **D.** Output voltage = 0Vstate

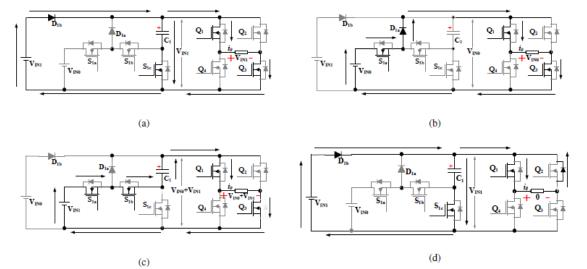

To get zero level atthe yield after the positive half cycle(Fig. 2 (d)), justtransistor Q1 is turned ON, whilethe various switches in the H-connect inverter stay killed. The body diode of transistorQ2 is utilized for nothing wheeling. Likewise, to acquire zero level at the yield after the negativehalf cycle, just transistorQ4 is turned ON, while the variousswitchesinthe full extension inverter stay killed. Forthis situation, the

body diode of transitorQ3 isutilized for freewheeling.The operational waveforms for the proposed 7 level inverter are appeared in Fig. 3. Utilizing these waveforms, it is conceivable to further understand the working conditions of the SCMLI. In the event that

VIN0 = 48V and VIN1 = 24V, the yield voltage waveform would have 0,  $\pm 24V$ ,  $\pm 48V$  and  $\pm 72V$ . The voltage over the capacitor C1, would consistently steady at 24V.

TABLEI:Switching rationale forthe 7-level SCMLI

TABLE I: Switching logic for the 7-level SCMLI

| $S_{1a}$ | $S_{1b}$ | $S_{1c}$ | $Q_1$ | $Q_2$ | $Q_3$ | $Q_4$ | $V_0$                    |

|----------|----------|----------|-------|-------|-------|-------|--------------------------|

| 0        | 0        | 1        | 1     | 0     | 1     | 0     | $V_{IN_1}$               |

| 1        | 0        | 0        | 1     | 0     | 1     | 0     | $V_{IN_0}$               |

| 1        | 1        | 0        | 1     | 0     | 1     | 0     | $V_{IN_0} + V_{IN_1}$    |

| 0        | 0        | 1        | 1     | 0     | 0     | 0     | 0                        |

| 0        | 0        | 1        | 0     | 1     | 0     | 1     | - V <sub>IN1</sub>       |

| 1        | 0        | 0        | 0     | 1     | 0     | 1     | - V <sub>IN2</sub>       |

| 1        | 1        | 0        | 0     | 1     | 0     | 1     | $-(V_{IN_0} + V_{IN_1})$ |

| 0        | 0        | 1        | 0     | 0     | 0     | 1     | 0                        |

### E. Enhancement in voltagelevels

Tofurther upgrade the quantity of yield levels, extra info voltagesources, capacitors

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

and switches must be utilized. A summed up SCMLI got from the proposed 7 level inverter is appeared inFig.4. For instance, if VIN0 = 40V, VIN1 = 20V & VIN2 = 10V, utilizing the exchanging rationale in Table II, a yield voltagestaircase waveform with qualities 0,  $\pm 10V$ ,  $\pm 20V$ ,...., $\pm 70V$  can be gotten. For this situation, C1 and C2 will be charged to 20V&10V separately. Fundamental unit required to understand the 15 level inverterfrom 7 levelinverter is divided utilizing dabbed lines. So also, if the featured unit is added to 15-levelinverter, a 31level inverter canbe figured it out. The most extreme voltage over theDC transport increments including extra information voltagesources. In any case, ideal number of sources mustbe included to such an extent that the DC transport voltage is inside reasonable point of confinement and does not instigate exceptionally highvoltage worry to the H-connect transistors. Number of individual segments in SCMLI canbe spoken to w.r.t the quantity of info voltage sources. On the off chance that the quantity of individual info voltagesources utilized in the MLI is signified by 'I', at that point the number ofoutput levels (nl), number ofSCs (n),number oftransistors (nT) andtheir entryway drivers (ngd), numberofdiodes (nD) are given by (1) to (4) separately.

$$n_l = 2^{i+1} - 1 \tag{1}$$

$$n = i - 1$$

(2)

$n_T = n_{gd} = 3i + 1$  (3)

$$n_D = 2(i-1)$$

(4)

Eqns.(1)to(4) canbe checked utilizing the proposed 15level inverter appeared in Fig. 4. SCMLItopology with highernumber of voltagelevels without utilizing extra voltage sources is displayed in [29]. It utilizes a SC kilter voltagesources (VIN1) to acknowledge twovoltage levels from solitary source. [30] proposes a seven level inverter utilizing two inconsistent voltage sources constrained to lowvoltage and lowpower applications.

Fig. 4: Generalized topology of the proposed SCMLI

TABLE II: Switching logic to realize a 15-level SCMLI from the generalized topology

| $S_{1a}$ | $S_{1b}$ | $S_{1c}$ | $S_{2a}$ | $S_{2b}$ | $S_{2c}$ | $V_{DCBUS}$                      |

|----------|----------|----------|----------|----------|----------|----------------------------------|

| 0        | 0        | 0        | 0        | 0        | 1        | $V_{IN_2}$                       |

| 0        | 0        | 1        | 1        | 0        | 0        | $V_{IN_1}$                       |

| 0        | 0        | 1        | 1        | 1        | 0        | $V_{IN_2} + V_{IN_1}$            |

| 1        | 0        | 0        | 1        | 0        | 0        | $V_{IN_0}$                       |

| 1        | 0        | 0        | 1        | 1        | 0        | $V_{IN_0} + V_{IN_2}$            |

| 1        | 1        | 0        | 1        | 0        | 0        | $V_{IN_0} + V_{IN_1}$            |

| 1        | 1        | 0        | 1        | 1        | 0        | $V_{IN_0} + V_{IN_1} + V_{IN_2}$ |

# IV. MODULATION FOR THE PROPOSEDINVERTER

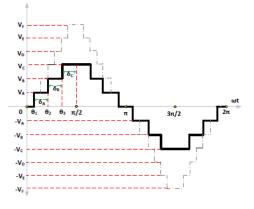

Particular Harmonic Elimination (SHE) [33] is a well known procedure which disposes of explicit sounds inthe yield. For Fourier examination, consider a 'm'level staircase waveform as appeared inFig.5. With co-

A Peer Revieved Open Access International Journal

www.ijiemr.org

efficientsa0and a being equivalent canbe scientifically spoken toas:

$$v(\omega t) = \sum_{x=1,3,5} \left( \frac{8}{T} \int_0^{T/4} f(\omega t) \sin(x\omega t) d\omega t \right) \sin(x\omega t)$$

$$= \sum_{x=1,3,5} \frac{4V_{IN}}{x\pi} \{ \cos x\theta_1 + \dots + \cos x\theta_z \} \sin(x\omega t)$$

(5)

where, z = (m-1)/2 and  $\theta_1$  to  $\theta_z$  are the conducting angles. The fundamental voltage in terms of switching angles is given by:

$$v_1(\omega t) = \frac{4V_{IN}}{\pi} \{ \cos\theta_1 + \dots + \cos\theta_z \} \sin(\omega t) \tag{6}$$

The maximum value of fundamental amplitude  $(V_{1p})$  isobtained when the all switching angles are equal to zero.

$$V_{1p} = \frac{4z}{\pi} V_{IN} \tag{7}$$

SHE processes conduction plots for a given regulation list to dispense with explicit music. For instance, in a 7 level inverter, just a limit of two music can be killed. Tweak list (MI) is characterized as the proportion of the ideal central voltage (V1) to the greatest realistic essential voltage.

$$M_I = \frac{V_1}{V_{1p}} = \frac{\pi V_1}{4z V_{IN_1}} \tag{8}$$

The harmonic equationstoeliminate5<sup>th</sup> and 7<sup>th</sup> harmonic for the proposedsevenlevel SCMLI are given as follows.

$$\begin{cases} \cos\theta_1 + \cos\theta_2 + \cos\theta_3 = 3M_I\\ \cos5\theta_1 + \cos5\theta_2 + \cos5\theta_3 = 0 \qquad (9)\\ \cos7\theta_1 + \cos7\theta_2 + \cos7\theta_3 = 0 \end{cases}$$

where,

$$0 < \theta_1 < \theta_2 < \theta_3 < \frac{\pi}{2} \qquad (10)$$

For  $M_I = 0.84$ , theangles, in degrees, computed usingselective harmonic eliminationare : $\theta_1 = 15.6^\circ$ ,  $\theta_2 = 18.7^\circ$

Fig. 5: Generalized staircase and 7 level ideal output voltage waveform

and  $\theta_3 = 52.4^{\circ}$ . With 5<sup>th</sup> and 7<sup>th</sup> harmonics eliminated, totalharmonic distortion (THD) can be given by:

$$T.H.D = \sqrt{\left(\frac{V_{rms}}{V_{1rms}}\right)^2 - 1} = \sqrt{\sum_{n=3,9,11,13..}^{\infty} \left(\frac{V_n}{V_{1rms}}\right)^2}$$

(11)

### V. CIRCUIT CHARACTERISTICS ANDANALYSIS

For investigation, it is expected that all indistinguishable transistorsare with equivalentonstate protections (RdsON), the protections inside (Rin) of the voltagesources equivalent andthe are forward voltage drop (VF) both the diodes are the equivalent. Forthe proposed SCMLI withI-input voltagesources, nlvoltage levels can be created (1). Under perfect case, every voltagelevel staircase (VA,VB,...) and capacitor voltage (VCi) can be communicated utilizing the accompanying arrangement of summed up conditions:

$$\begin{cases}

V_A = V_{IN_t} \\

V_B = V_{IN_{t-1}} \\

V_C = V_{IN_t} + V_{IN_{t-1}} \\

V_D = V_{IN_{t-2}} \\

V_E = V_{IN_{t-2}} + V_{IN_t} \\

V_F = V_{IN_{t-2}} + V_{IN_{t-1}} \\

\dots \\

\dots \\

V_U = V_{IN_t} + V_{IN_{t-1}} + \dots + V_{IN_0} \\

V_{C_t} = V_{IN_t}

\end{cases}$$

(12)

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

General expressionforRMSvalueofthe mlevel staircase waveform isgivenby:

$$V_{0_{RMS}} = \sqrt{\frac{2}{\pi} \left( V_A^2 \delta_A + V_B^2 \delta_B + \dots + V_N^2 \delta_N \right)}$$

(13)

Outputwaveform is symmetric when the magnitude of inputvoltagesources are integralmultiples of magnitude of the least value of input voltage source. That is, for a 7leveloutput if  $V_{IN0} = kV_{IN1}$ , where k is a greater than 1. Then,  $V_{0RMS}$  of the 7levelwaveform shown in Fig. 5 is:

$$V_{0_{RMS}} = V_{IN_1} \sqrt{\frac{2}{\pi} (\delta_A + k^2 \delta_B + (k+1)^2 \delta_C)}$$

(14)

Considering non-idealities  $R_{in}$ ,  $V_F$ ,  $R_{dsON}$  and ESR of the SC, each voltage step and the  $V_{C1}$  of the 7 level inverter can be represented as

$$\begin{cases} V_A = V_{IN_1} - V_F - I_o(2R_{dsON} + R_{in}) \\ V_B = kV_{IN_1} - V_F - I_o(3R_{dsON} + R_{in}) \\ V_C = kV_{IN_1} + V_{C1} - I_o(4R_{dsON} + R_{in} + ESR) \\ V_{C1} = V_{IN_1} - V_F - I_{c1}(R_{dsON} + R_{in} + ESR) \end{cases}$$

(15)

where, Io is the normal yield current of the front-end converter and Ic1 is the normal capacitor chargingcurrent. Eqn. (15) proposes to pick transistors withlowRdsON, diodes with VF and lowESR capacitors forbetter use accessible voltagesource and improved productivity.

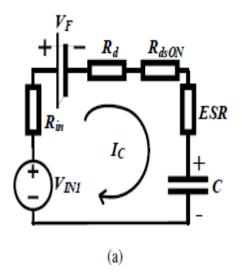

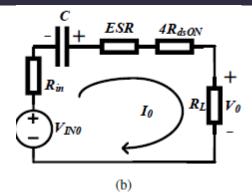

### A. Switched-capacitor analysis

SC is the singular vitality stockpiling component for the proposed SCMLI. It is, along these lines, basic to choose the fitting estimation capacitance of for the application. The estimation of the capacitance more often than not relies upon the recurrence of activity, greatest burden current prerequisite and as far as possible forced on he swell voltage. Under perfect capacitor C1 is charged to VIN1 when associated inparalleltothe source and released tothe heap when associated in arrangement with VIN0, as clarified in Fig. 2. Thinking about perfect conditions, C1 is charged to VIN1 during  $V0 = \pm VIN1$  and V0 = 0V states and released uniquely during V0 =  $\pm$ (VIN0+VIN1) state. Be that as it may, actually the yield voltage levels are lower than the info voltages as clarified in (15).

The releasing of C1 is started just whenswitches S1a and S1b of the frontendSC DC-DCconverter are turnedON. The releasing time frame closes when both are killed. During releasing, C1 alongside VIN1 supply vitality to the heap. On the off chance that the most extreme burden current isknown, this releasing period canbe utilized to decide the ideal estimation of SC foragivenvoltage swell point of confinement. On the off chance that QC is the measure of charge discharged by C1 during the period at that point

$$Q_C = \int_{t_{d1}}^{t_{d2}} I_0 \sin(2\pi f_s t - \phi) dt$$

(16)

where, the limits  $t_{d1}$  and  $t_{d2}$  correspond to the discharging period,  $I_0$ is the maximumvalueofoutput current  $(i_0(t)),$  $f_s$  is the fundamental frequency and  $\phi$  is the phase difference between the voltage&current. Ripple voltage ( $\Delta V_C$ ) canbe calculated using the angles computed bySHE using

$$\Delta V_C = \frac{1}{2\pi f_s C} \int_{\theta_t}^{\pi - \theta_t} I_0 \sin(2\pi f_s t - \phi) d\omega t \qquad (17)$$

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

### Fig. 6: Equal circuits of sevenlevelSCMLI during (a) capacitorcharging (b) capacitorreleasing

where,  $\theta_i$  is the edge at which the capacitor begins to release and  $\pi - \theta_i$  is the point at which the releasing stops. On the off chance that p(%) is the farthest point forced on the swell voltage ( $\Delta V_C$ ), at that point C can be picked dependent on the accompanying condition.

$$C \ge \frac{Q_C}{pV_{IN1}} \tag{18}$$

Voltage rating of a capacitor additionally assumes an indispensable job. All in all, as the estimation of capacitance builds, the physical elements of the capacitor additionally increment which makes the converter massive. Along these lines, it is imperative to pick an ideal estimation of capacitance considering all the previously parameters. Most mentioned makers' datasheet give dispersal factor (DF) as a proportion of execution. DF, in basic terms is the proportion of vitality misfortune to the vitality put away in a capacitor. Accepting, zero parasitic inductance, ESR of an electrolytic capacitor regarding DF is given by

$$ESR = \frac{DF}{2\pi f_s C} \tag{19}$$

where  $DF = tan\delta$ ,  $\delta$  s the misfortune edge between capacitor's impedance vector and the negative reactance pivot. Lower DF is a proportion of unrivaled quality among capacitors when comparative di-electric materials are utilized. It is hence prescribed to pick an enormous enough SC to limit ESR. Lower ESR diminishes voltage drop and conduction misfortune.

### **B.** Loss Analysis

1) Conduction Loss: In the SC, it is because of intensity dispersal in the ESR. In the proposed 7 level SCMLI, capacitor

$C_1$  is charged near to  $V_{IN1}$  when  $S_{1c}$  is turned ON.

The vitality put away is released to the heap when  $S_{1a}$  and  $S_{1c}$  are turned ON keeping  $S_{1b}$ OFF. The greatest capacitor charging current ( $I_{Cch(m)}$ ), found from Fig. 6 (an), is given by

$$I_{C_{ch(m)}} = \frac{V_{IN1} - V_F - V_{ci}}{R_d + R_{in} + ESR + R_{ds_{ON}}} = \frac{V_{eq}}{R_{eq}}$$

(20)

where,  $V_{ci}$  is the initial capacitor voltage,  $V_{eq} = V_{IN1} - VF - VciandReq = Rd + Rin + ESR + RdsON$ . At the point when the distinction among VIN1 and the underlying capacitor voltage between  $V_{IN1}$  and the initial capacitor voltage

$(V_{ci})$  is lower,  $I_{CCH(M)}$  is likewise decreased. This mitigates spiky current waveforms. In this way, a huge enough capacitor must be picked to decrease undesired pinnacle flows. Smooth waveforms during charging draw out the life of the SC. The charging normal for the capacitor can be spoken to as

$$i_{C_{ch}}(t) = I_{C_{ch}(m)} e^{t/R_{eq}C}$$

(21)

where tis charging time. In the 7 level SCMLI,  $C_1$  is charged twice every cycle. On the off chance that charging span $\Delta t = t_2-t_1$ ,  $I_{CchRMS}$  is given by

$$I_{C_{chRMS}} = \sqrt{\frac{2}{T} \int_{t_1}^{t_2} i_{C_{ch}}^2(t) dt}$$

(22)

The conduction loss during charging of C for the 7 level SCMLI can be given as

A Peer Revieved Open Access International Journal

(23)

www.ijiemr.org

$$P_{con(ch)} = I_{C_{chRMS}}^2 ESR$$

$$I_{C_{disRMS}} = I_{0_{RMS}} = \frac{1}{R_L} \sqrt{\frac{2}{\pi} \left( V_A^2 \delta_1 + V_B^2 \delta_2 + V_C^2 \delta_3 \right)}$$

(24)

where,  $V_A$ ,  $V_B$  and  $V_C$  are assumed by (12). The conduction damage during clearing is given by

$$P_{con(dis)} = I_{0_{RMS}}^2 ESR \tag{25}$$

Conduction misfortune in the transistors is because of the warmth disseminated inR<sub>dsON</sub>during stream. current Correspondingly, diode obstructionR<sub>d</sub> additionally brings about conduction misfortune. Hence, it is critical to pick parts with low inward protections from lift working productivity. The net conduction shortfall in transistor  $(P_{con(T)})$  and diode  $(P_{con(D)})$  are given by

$$P_{con(T)} = \sum_{i=1}^{n_T} I_{T_i RMS}^2 R_{ds_{ON}}$$

(26)

$$P_{con(D)} = \sum_{i=1}^{n_D} I_{D_i RMS}^2 R_d$$

(27)

2) Switching Loss: It is because of continued charging and releasing of parasitic capacitance ( $C_T$ ) in the transistors.  $C_T$  is charged to  $V_T$  when the transistor is killed and releases when the transistor turns ON. This prompts covering of transistor's voltage and current waveform twice every cycle causing vitality misfortune. For investigation, accept turn-on and turn-off covering times are equivalent ( $T_{ov}$ ), voltage and current have direct connections as beneath.

$$i(t) = I_{Ton}(1 - \frac{t}{T_{ov}})$$

(28)

$$v(t) = V_T \frac{t}{T_{ov}} \tag{29}$$

For each exchanging cycle, two covering – one during transistor turn-on and one during mood killer happen. At that point, control misfortune per transistor during the covering time frame is given by  $P_{sw(Ton)} = f_s \int_0^{T_{ov}} v(t)i(t) = \frac{V_T I_{Ton} f_s T_{ov}}{6}$ (30)

Similarlyswitchingdamage during turn-off isgiven.

$$P_{sw(Toff)} = \frac{V_T I_{Toff} f_s T_{ov}}{6}$$

(31)

where,  $I_{Toff}$  is the current throu the transistor before turn OFF. Switching damage in diodes is due to the inverse recovery [34] is given by

$$P_{sw(D)} = \frac{V_D I_{rrp} f_s t_r}{6} \tag{32}$$

where,  $t_r$  is the time taken by the switch recuperation current to tumble from its pinnacle estimation of  $I_{rrp}$  to zero when a voltage of  $V_D$  is connected over the diode. Proficiency can be determined by:

$$\eta_{eff} = 1 - \frac{P_L}{P_{in}} \tag{33}$$

where  $P_{in}$  is the input power and  $P_L$  is the total powerloss.

### VI. COMPARISONS WITH CONVENTIONAL MULTILEVEL INVERTERS AND OTHERSCMLI TOPOLOGIES

SCMLI has a few preferences customary topologies. Diode clasped MLI requests a high voltage rating for blocking diodes. As quantity of levels builds, quantity of diodes makesthe inverter difficult tobe actualized. Capacitor terminals is extraordinary, the capacitorsreleased to various qualities results in voltage unbalance issue. Here issues are defeated in the proposed SCMLI.

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

DCI gets (2n + 3) levels for n capacitors utilized. Notwithstanding, the proposed **SCMLI** produces (2(n+2))-1) levels.Similarly, capacitor clasped MLI requires countless capacities. Along these lines, this element makes it over the top expensive and hard for bundle with cumbersome capacity capacitors. The significant downside of the fell H-connect (CHB) inverter is the requirement for independent detached DC sources. Likewise, high no. of transistors utilized in the hardware expands the expense. In examination, the proposed SCMLI utilizes less transistors to acquire a given number of levels. For e.g., CHB requires seven separate DC sources and twenty eight transistors (seven H-spans) to understand a 15level inverter though the proposed SCMLI just requires three sources, ten transistors and four diodes.For correlation with other SCMLI topologies utilizing seriesparallelIt is seen that the quantity of yield voltage levels increment exponentially with extra SCs and information voltage sources. Be that as it may, different topologies have a straight connection between the quantity of SCs and the yield voltage levels. The voltage weight on the Hconnect transistors the ability to drive inductive burdens is restricted like generally topologies. The stage distinction between the yield voltage and current can't be more prominent than  $\varphi = \theta 1$ . To oblige bigger inductive burdens, the proposed SCMLI can be worked at lower regulation indices. The traditional Fibonacci SC DC-AC inverters appeared in Fig. 1 of [27] utilize a bigger number of segments than the novel inverter proposed in Fig. 2 of [27]. To understand a 15 level (7 x venture up) staircase waveform, the ordinary SC DC-AC converter utilizes sixteen SC and sixty two transistors where as novel Fibonacci inverter utilizes eight SC, twenty four transistors and six diodes. In correlation, the proposed SCMLI requires just two SC, ten transistors and four diodes. Be that as it may, it utilizes three inconsistent voltage sources.Operating proficiency of any power converter relies upon an assortment of parameters. Expecting a similar nature of segments utilized, same PWM technique, comparative working conditions and cooling courses of action, the examination of effectiveness is done regarding the quantity of parts utilized for a given number of ventured yield voltage levels. In Table III, the quantity of parts utilized in the proposed converter is contrasted and other SCMLI with Hbridge topologies. Topology from [25] utilizes the base number of switches (transistors diodes). In this way, it is contrasted and the proposed topology with indistinguishable reenactment parameters from appeared in segment VII. For the topology from [25], input voltage was fixed at 20 V to emulate the 60 V yield top trademark, comparable tothe proposed topology. Two instances of the proposed inverter were considered. In the main case, a DC - DC change stage is utilized to acquire the ideal estimation of the info voltages. In the subsequent case, the DC - DC transformation stage wasn't utilized. Under the two situations, the proposed inverter offered better proficiency at higher power levels. At lower power levels, the topology from [25] offered better proficiency. This is fundamentally a direct result of the quantity of SCs utilized by every topology. In [25], two SCs are utilized to acquire a seven level yield though the proposed topology utilizes just one. Because of the higher voltage progressively outstretching influence of SCs, the productivity of topology from [25] is lower. Another reason is that the proposed topology utilizes SC voltage to yield only

A Peer Revieved Open Access International Journal

www.ijiemr.org

two out of seven levels and the rest of the levels are legitimately bolstered by the DC sources; though the topology from [25] utilizes the SC voltage to yield five out of seven levels. This diminishes the voltage swell for the proposed topology empowering it to utilize littler SCs sparing expense and space.

### TABLE III: Comparison of series parallel based SCMLI topologies with H-bridg

|             | $n_T$  | $n_D$ | i   | $n_l$           | H-bridge stress        |

|-------------|--------|-------|-----|-----------------|------------------------|

| Fig. 2 [20] | 3n + 3 | n     | 1   | 2n + 3          | $(n+1)V_c$             |

| Fig. 1 [21] | 6n     | n     | n   | 4n + 1          | $nV_{IN}$              |

| Fig. 1 [22] | n+5    | 2n    | 1   | 2n + 3          | $(n + 1)V_c$           |

| Fig. 3 [23] | 2n + 4 | n     | 1   | 2n + 3          | $(n + 1)V_c$           |

| Fig. 1 [25] | 3n + 4 | 0     | 1   | 2n + 3          | $(n + 1)V_c$           |

| Fig. 2 [26] | 4n + 1 | n     | 1   | 4n + 1          | $nV_{in}$              |

| Proposed    | 3n + 4 | 2n    | n+1 | $2^{(n+2)} - 1$ | $\sum V_{ci}+V_{IN_0}$ |

TABLE IV: Harmonic content in the seven level output voltage waveform

| Harmonic       | Fundamental | $3^{rd}$ | $5^{th}$ | $7^{th}$ | $9^{th}$ | $11^{th}$ | 13 <sup>th</sup> |

|----------------|-------------|----------|----------|----------|----------|-----------|------------------|

| Simulation (V) | 62          | 3.5      | 0.1      | 0.1      | 5.85     | 5.95      | 1.26             |

| Measured (V)   | 60          | 3        | 1        | 1        | 6        | 7         | 2                |

So as to expand the productivity, higher estimation of SCs can be utilized as it proportionately diminishes the voltage swell. Be that as it may, misfortune because of ESR, space and cost elements must be considered. Additionally, as the quantity of levels expands, the weight on the voltage Hconnect inverter builds; a typical element to all H-connect SCMLI topologies surveyed. The proposed inverter is restricted to work just when there are numerous inconsistent voltage sources utilized. In the event that solitary a solitary voltage source is accessible, it is as yet conceivable to create another voltage level utilizing an exchanged capacitor doubler or exchanged capacitor based half circuit.

### VII. SIMULATION AND EXPERIMENTAL RESULTS

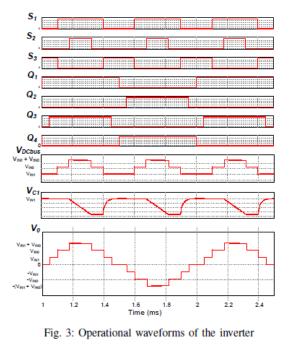

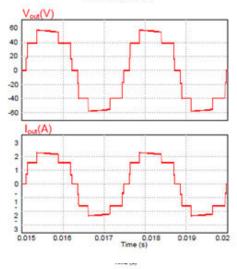

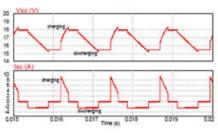

Reenactment of proposed SCMLI evaluated with VIN0 = 40V, VIN1 = 20V utilizing a 470 $\mu$ F SC is finished. Rin = 0.1 $\omega$ , ESR = 0.1 $\Omega$ , VF= 0.42V, Rd = 10m $\omega$ , RdsON=  $9m\omega$ ,  $\theta 1 = 15.6^{\circ}$ ,  $\theta 2 = 18.7^{\circ}$  and  $\theta 3 =$ 52.4° are considered for recreation. Fig. 7 (a) demonstrates the 7-level staircase yield voltage and current working at 400 Hz when a resistive heap of 25  $\Omega$  is associated. With increment in power levels, the abundancy of the staircase waveform lessens as the capacitor releases to a lower esteem each cycle. The capacitor charging and releasing qualities are appeared in Fig. 7(b). It very well may be obviously observed that the capacitor charges and releases twice each cycle. The capacitor charges to Vc1 as clarified in (15) and releases to a voltage esteem that is reliant on the heap current. Table IV demonstrates the predominant music in the yield.

TABLE V: Experiment specifications and components list

| Input voltage $(V_{IN0})$       | 40 V         |

|---------------------------------|--------------|

| Input voltage $(V_{IN1})$       | 20 V         |

| Output frequency $(f_S)$        | ≥ 400 Hz     |

| Switched-capacitor $(C_1)$      | 470 μF       |

| Transistors (N-channel MOSFETs) | FDB3632      |

| Diodes (Schottky Rectifier)     | NTST30U100CT |

| Maximum power                   | 250 W        |

| Controller                      | TMS320F28335 |

| Gate Drivers                    | IR2113       |

A Peer Revieved Open Access International Journal

www.ijiemr.org

Table V details the experiment specifications and the components employed. A simple algorithm is developed on

(b) Fig. 7: Simulation waveforms at 400 Hz including nonidealities : (a) output voltage and current (b) switched capacitor voltage and current

Fig. 8: Measured 400 Hz waveforms (a) Output voltage and current (b) Switched capacitor voltage and current

Fig. 9: Measured 1kHz, output with resistive loads. Ch. 1:Output voltage, Ch. 2: Output Current. (a) 37 W (b) 255

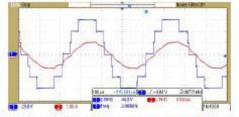

TMS320F28335 controller to execute SHE for the proposed SCMLI. Table VI demonstrates the estimations of  $\theta 1$ ,  $\theta 2$  and  $\theta$ 3 at various regulation records. Since the yield voltage of the SCMLI is a component of the balance record (8), the tweak list can be balanced continuous to understand the required extent of yield voltage. То understand this, a look table with benefits of exchanging plots for different MI ought to be modified into the DSP. The required tweak file can be picked relying upon whether the yield voltage should be ventured up or down, the data of which is acquired from the feedback.Simulation and exploratory consequences of seven level yield voltage and current, and SC voltage and current waveforms working at MI = 0.84 with yield recurrence of 400 Hz are appeared in Fig. 7 and Fig. 8 separately.

STOP

# International Journal for Innovative Engineering and Management Research

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

Fig. 10: Measured FFT with resistive loads. Ch. 1: Output voltage (use 2x multiplier), Ch. M: FFT plot. (a) 400 Hz (b)1000 Hz

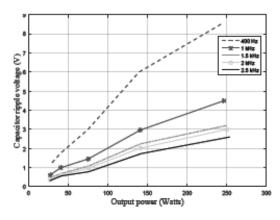

Fig. 9 (an) and (b) demonstrate the 7 level staircase yield voltage and current at 1 kHz working at 37 W and 255 W separately. It tends to be seen that the voltage drop increments at higher power activity. In the event that the voltage drop is extreme, the yield voltage is never again near the ideal staircase waveform. This expands the line sounds. Voltage drop at higher power levels can be decreased either by expanding the estimation of SC or by expanding the working frequency.FFT investigation of SCMLI's yield voltage waveforms working at 400 Hz and 1 kHz conveyance frequencies is appeared in Fig. 10 (an) and (b) separately and organized in Table IV. Utilizing SHE, fifth and seventh sounds are limited. Little extents of third, ninth and eleventh symphonious still exist. In the event that an ideal estimation of capacitor isn't picked for a given power level and vield recurrence. the symphonious substance in the yield waveform will increment and cause a few undesired impacts. Better adjustment plans can likewise be received to streamline the exchanged capacitor size for a given recurrence.

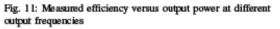

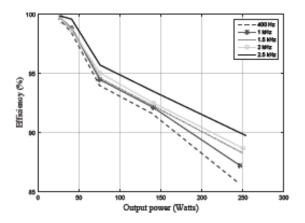

Fig. 11 of demonstrates the plot effectiveness versus yield control at various dissemination frequencies. It is seen that as the recurrence builds, the productivity of the inverter increments. This can be clarified from Fig. 12, which demonstrates the variety in SC swell voltage with recurrence and yield control. For a given power level, the conveyance recurrence expanding decreases the SC swell voltage, in this way improving the working

TABLE VI: SHE exchanging plots for various modulationindicesefficiency.

| M <sub>I</sub> | $\theta_1$ | $\theta_2$ | $\theta_3$ |

|----------------|------------|------------|------------|

| 0.5            | 39.4°      | 56.25°     | 80.1°      |

| 0.6            | 11.8°      | 41.7°      | 85.7°      |

| 0.7            | 18.3°      | 44.1°      | 64.4°      |

| 0.84           | 15.6°      | 18.7°      | 52.4°      |

| 0.92           | 7.98°      | 15.3°      | 36.4°      |

To further relieve exchanging misfortunes, a full front-end SC converter can be planned by adding an arrangement inductor to acknowledge zero current exchanging. Be that as it may, this will expand the voltage weight on the gadgets employed.Fig. 13 demonstrates the yield waveforms with inductive burden. An inductor is associated in arrangement with a variable resistor as the heap. For the investigation, L = 1 mH, R = 58  $\Omega$  was utilized. The estimation of the stage edge is equivalent to 15.15°. It very well may be seen that the yield voltage is like that with R load. Notwithstanding, the present waveform is increasingly sinusoidal.

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

This waveform approves that the proposed SCMLI can fill in as a HF source to control inductive burdens with a little stage contrast and is for the most part pertinent in high power factor applications or providing dynamic capacity to microgrids from sustainable power source ranches. Nonetheless, Table VI infers that at low tweak lists a bigger inductive burden can be upheld.

### **VIII. DISCUSSION**

Consider a case of an electric golf-vehicle (characterized under little vehicle). Whenever inputvoltage from the sources are beneath48V, it fallsunder the class of safe working voltages. This thus mitigatesthe general expense as it disposes of the need to introduce costly high voltage defensive highlights. Thusly, the essential battery is normally evaluated underneath 48 V DC. Also, present day golf-vehicles outfitted with sun based boards charge the assistant battery to a lower estimation of around 20 V. Another model is the half and half electric vehicle fueled by Liion batteries and super-capacitors. Since the ostensible voltage of Li-particle battery is 3.7 V and that of super-capacitor is 2.7 V, the voltage levels of these arrangement associated vitality stockpiling gadgets will undoubtedly vary. Both these separate sets of voltage sources can be utilized as contributions to produce a high recurrence AC dissemination line. The high recurrence AC power is redressed before driving the DC engine and different burdens. In the proposed SCMLI, if the distinction between the two information voltage sources isn't enormous enough, at that point the preferences lessen. Be that as it may, with higher voltage levels the expense of usage increments as there is a need to include defensive highlights for high voltage activity. Future work incorporates

exploring PWM strategies to upgrade THD levels for inconsistent voltage steps.

#### **IX. CONCLUSION**

The topology is appropriate inconsistent DC information sources areat transfer. Such situations are normal enormous sustainable power source homesteads and electric vehicle systems. It progressively advantageous to utilize numerous DC sourcesas contribution to solitary inverter than to utilize a few invertersinparallel with their individual single DC information sources.

Fig. 12: Measured peak to peak capacitor ripple voltage versus output power at different output frequencies

Here topology does not pile upthe voltage sources arrangement &in this manner does notrequire voltage adjusting circuits. Sincethe exchanged capacitors utilized duplicate info voltage each cycle, the issue of voltage adjusting has additionally been

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

killed. The consonant substance waveform is dissected and is observed to least. The specified topology gets high number of voltage levels contrasted with a few existing topologies. In the article uses the specified topology for higher recurrence AC appropriation. Nonetheless, a similar topologies can be utilized for50Hz/60Hz appropriation by utilizing a bigger exchanged capacitor. Here demonstrated thatthe quantity of yield voltagelevels exponentially increment with increment in the utilized info. In the equipment results, it is demonstrated that the 5<sup>th</sup> ,7<sup>th</sup>music are limited to very lowvalue of 1V each. Resultsat various dispersion frequencies&powerlevelsare exhibited.

Fig. 13: Measured 2.5 kHz waveforms with inductive load. Ch. 1 : Output voltage, Ch. 2: Output Current

#### REFERENCES

- Patel, MukundR.,"High-Power High-Voltage Systems", Spacecraft Power Systems, CRC press, 2004, ch. 22, sec. 22.7, pp. 539-543.

- Luk, Patrick Chi-Kwong, and Andy SengYim Ng. "High Frequency AC Power Distribution Platforms." Power Electronics in Smart Electrical Energy Networks. Springer London, 2008. pp. 175-201.

- Z.Ye,P.K.Jain and P.C.Sen, "A Two-Stage Resonant Inverter With Control of the Phase Angle and Magnitude of the Output Voltage," in IEEE Trans. Ind. Electron., vol. 54, no. 5, pp. 2797-2812, Oct. 2007.

- 4. J.A.Sabate,M.M.Jovanovic,F.C.Lee and R.T.Gean, "Investigation and structure

enhancement of LCC thunderous inverter for high-recurrence AC appropriated control framework," in IEEE Trans. Ind. Electron., vol. 42, no. 1, pp. 63-71, Feb 1995.

- 5. Status of 20 kHz SpaceStationPower Distribution Technology,NASA Publication, TM100781.

- S.Tsai,F.C.Y.Lee, "High-recurrence AC control appropriation in Space Station," in IEEETrans on Aerospace &Electronic Systems, vol.26,no.2,pp.. 239-253,Mar1990.

- Antaloae, J. Marco, N.D. Vaughan, "Attainability of HighFrequency Alternating Current Power for Motor Auxiliary Loads in Vehicles," in IEEE Trans. Vehicular Technology, vol. 60, no. 2, pp. 390405, Feb. 2011.

- M.A.Masrur, D.S.Sitar and V.A.Sankaran, "Can an AC (substituting flow) electrical framework supplant the present DC framework in the car? An analytical achievability study. II. Examination and tradeoffs," in IEEE Trans. Vehicular Technology, vol. 47, no. 3, pp. 1081-1086, Aug 1998.

- S.RaghuRaman, et.al, "High recurrence AC helper power hotspot for future vehicles", 2015 sixth International Conference on Power Electronics Systems & Applications(PESA), Hong Kong,2015,pp.1-6.

- Bose, Min-HueiKin and M.D.Kankam, "High recurrence AC versus DC dispersion framework for cutting edge half breed electric vehicle," Industrial Electronics, Control, &Instrumentation, Proceedings of the 1996 IEEEIECON 22ndInternational Conferenceon, Taipei, 1996, pp. 706-712vol.2.

- 11. S.Chakraborty, M.D.Weiss and M.G. Simoes, "Dispersed Intelligent

A Peer Revieved Open Access International Journal

www.ijiemr.org

12. Energy Management System for a Single-Phase High-Frequency AC Microgrid," in IEEETrans.Ind. Electron.,vol.54,no.1,pp.97-109, Feb.2007.