A Peer Revieved Open Access International Journal

www.ijiemr.org

### COPY RIGHT

**2019IJIEMR**. Personal use of this material is permitted. Permission from IJIEMR must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 16<sup>th</sup> Nov 2019. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-08&issue=ISSUE-11

Title IMPLEMENTATION OF FAST FOURIER TRANSFORM (FFT) USING ALGORITHMIC BASED FAULT TOLERANCE (ABFT) TECHNIQUES

Volume 08, Issue 11, Pages: 41–47.

Paper Authors

### K.PRADEEP, CH.KUTUMBA RAO

VAHINI INSTITUTE OF SCIENCE & TECHNOLOGY TIRUVURU, KRISHNA DIST, ANDHRA PRADESH, INDIA.

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

### IMPLEMENTATION OF FAST FOURIER TRANSFORM (FFT) USING ALGORITHMIC BASED FAULT TOLERANCE (ABFT) TECHNIQUES <sup>1</sup>K.PRADEEP, <sup>2</sup>CH.KUTUMBA RAO

<sup>1</sup>PG SCHOLAR, VAHINI INSTITUTE OF SCIENCE & TECHNOLOGY <sup>2</sup>PROFESSOR DEPARTMENT OF ECE IN VAHINI INSTITUTE OF SCIENCE &TECHNOLOGY TIRUVURU, KRISHNA DIST, ANDHRA PRADESH, INDIA.

### **ABSTRACT:**

Delicate blunders represent an unwavering quality danger to present day electronic circuits. This makes security against delicate mistakes a necessity for numerous applications. Correspondences and sign preparing frameworks are no special cases to this pattern. For certain applications, a fascinating alternative is to utilize algorithmic-based adaptation to non-critical failure (ABFT) procedures that attempt to abuse the algorithmic properties to recognize and address blunders. Signal preparing and correspondence applications are appropriate for ABFT. One model is quick Fourier changes (FFTs) that are a key building hinder in numerous frameworks. A few security plans have been proposed to ecognize what's more, right blunders in FFTs. Among those, presumably the utilization of the Parseval or then again whole of squares check is the most broadly known. In present day correspondence frameworks, it is progressively basic to discover a few squares working in parallel. As of late, a procedure that endeavors this reality to execute flaw resistance on parallel channels has been proposed. In this concise, this procedure is first applied to secure FFTs. At that point, two improved insurance plans that consolidate the utilization of blunder redress codes and Parseval checks are proposed and assessed. The outcomes show that the proposed plans can further decrease the usage cost of insurance.

### **INTRODUCTION:**

The intricacy of interchanges and sign preparing circuits expands each year. This is made conceivable by the CMOS innovation scaling that empowers the coordination of to an ever increasing extent transistors on a solitary gadget. This expanded multifaceted nature makes the circuits progressively powerless against blunders. Simultaneously, the scaling implies that transistors work with lower voltages and are progressively powerless to blunders brought about by commotion and assembling varieties [1]. The significance of radiation-prompted

delicate mistakes likewise increments as innovation scales [2]. Delicate mistakes can change the sensible estimation of a circuit hub making an impermanent mistake that can influence the framework activity. To guarantee that delicate blunders don't influence the activity of a given circuit, a wide assortment of systems can be utilized [3]. These incorporate the utilization of uncommon assembling forms for the coordinated circuits like, for instance, the silicon on separator. Another choice is to fundamental circuit plan squares or

A Peer Revieved Open Access International Journal

www.ijiemr.org

complete structure libraries to limit the likelihood of delicate blunders. At long last, it is additionally conceivable to include excess at the framework level to distinguish and address blunders. One traditional model is the utilization of triple secluded repetition (TMR) that triples a square and votes among the three yields to recognize what's more, right mistakes. The fundamental issue with those delicate blunders alleviation strategies is that they require an enormous overhead as far as circuit execution. For instance, for TMR, the overhead is >200%. This is on the grounds that the unprotected module is duplicated multiple times (which requires a 200% overhead versus the unprotected module), what's more, furthermore, voters are expected to address the mistakes making the overhead >200%. This overhead is unnecessary for some applications. Another methodology is to attempt to utilize the algorithmic properties of the circuit to distinguish/right blunders. This is ordinarily alluded to as calculation based adaptation to internal failure (ABFT) [4]. This technique can decrease the overhead required to ensure circuit. Signal preparing and а correspondences circuits are appropriate for ABFT as they have standard structures and algorithmic numerous properties [4]. Throughout the years, numerous ABFT methods have been proposed to secure the essential hinders that are normally utilized in those circuits. A few works have thought about the insurance of computerized channels [5], [6]. For instance, the utilization of replication utilizing decreased exactness duplicates of the channel has been proposed as an option to TMR yet with a lower cost [7]. The information on the

conveyance of the channel yield has likewise been as of late misused to recognize and right mistakes with lower overheads [8]. The security of quick Fourier changes (FFTs) has likewise been broadly examined [9], [10]. As sign preparing circuits become progressively unpredictable, it is basic to discover a few channels or FFTs working in parallel. This happens for instance in channel banks [11] or in various information numerous vield (MIMO) correspondence frameworks [12]. Specifically, MIMO symmetrical recurrence adjustment division (MIMO-OFDM) frameworks utilize parallel iFFTs/FFTs for adjustment/demodulation [13]. MIMO-**OFDM** is executed on long haul development portable frameworks [14] and furthermore on WiMax [15]. The nearness of parallel channels or FFTs makes a chance to execute ABFT procedures for the whole gathering of parallel modules rather than for every one freely. This has been read for advanced channels at first in [16] where two channels were considered. All the more as of late, a general conspire dependent on the utilization of mistake adjustment codes (ECCs) has been proposed [17]. In this procedure, the thought is that each channel can be what could be compared to a piece in an ECC and equality check bits can be processed utilizing expansion. This system can be utilized for activities, in which the yield of the total of a few sources of info is the whole of the individual yields. This is valid for any direct activity as, for model, the discrete Fourier change (DFT). In this concise, the assurance of parallel FFTs is examined. Specifically, it is expected that there must be a solitary mistake on the

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

framework at any given point in time. This is a typical presumption while considering the insurance against radiation-instigated delicate mistakes [3]. There are three fundamental commitments in this brief.

1) The assessment of the ECC system [17] for the security of parallel FFTs demonstrating its adequacy as far as overhead also, assurance adequacy.

2) The proposition of another system dependent on the utilization of Parseval or whole of squares (SOSs) checks [4] joined with an equality FFT.

3) The proposition of another system on which the ECC is utilized on the SOS checks rather than on the FFTs.

The two proposed systems give new choices to secure parallel FFTs that can be more proficient than securing each of the FFTs autonomously.

The proposed plans have been assessed utilizing FPGA usage to evaluate the insurance overhead. The outcomes show that by joining the utilization of ECCs and Parseval checks, the security overhead can be diminished contrasted and the utilization of just ECCs as proposed in [17]. Deficiency infusion tests have likewise been directed to check the capacity of the executions to recognize and right mistakes.

The remainder of this brief is composed as pursues. Segment II presents the two proposed plans. In Section III, the execution overheads what's more, adaptation to internal failure of the plans are assessed. At long last, the ends are attracted Section IV.

### PROPOSED PROTECTION SCHEMES FOR PARALLEL FFTS

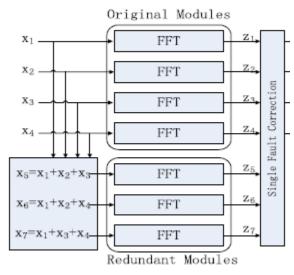

The beginning stage for our work is the assurance plot based on the utilization of ECCs that was displayed in [17] for computerized channels. This plan is appeared in Fig. 1. In this model, a basic single blunder redress Hamming code [18] is utilized. The first framework comprises of four FFT modules and three excess modules is included to recognize and address mistakes. The contributions to the three excess modules are straight blends of the information sources and they are utilized to check straight blends of the yields. of the quantity of unique FFTs. For instance, to secure four FFTs, three redudant FFTs are required, yet to ensure eleven, the quantity of excess FFTs in just four. This shows how the overhead diminishes with the quantity of FFTs. In Section I, it has been referenced that throughout the years, numerous systems have been proposed to secure the FFT. One of them is the Entirety of Squares (SOSs) check [4] that can be utilized to distinguish blunders. The SOS check depends on the Parseval hypothesis that expresses that the SOSs of the contributions to the FFT are equivalent to the SOSs of the yields of the FFT aside from a scaling factor. This relationship can be utilized to

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

distinguish mistakes with low overhead as one augmentation is required for each information or yield test (two duplications and adders for SOS per test). For parallel FFTs, the SOS check can be joined with the ECC way to deal with lessen the security overhead. Since the SOS check can just identify mistakes, the ECC part ought to have the option to actualize the adjustment. This should be possible utilizing what could be compared to a straightforward equality bit for all the FFTs. Furthermore, the SOS check is utilized on each FFT to recognize mistakes. At the point when a blunder is identified, the yield of the equality FFT can be utilized to address the mistake. This is better clarified with a model. In Fig. 2, the first proposed plan is delineated for the instance of four parallel FFTs. An excess (the equality) FFT is included that has the total of the contributions to the first FFTs as input. A SOS check is additionally added to every unique FFT. In the event that an blunder is recognized (utilizing P1, P2, P3, P4), the revision should be possible by recomputing the FFT in blunder utilizing the yield of the equality FFT (X) and the remainder of the FFT yields. For instance, if a blunder happens in the first FFT, P1 will be set and the mistake can be amended by doing This combination of a parity FFT and the SOS check reduces the number of additional FFTs to just one and may, therefore, reduce the protection overhead. In the following, this scheme will be referred to as parity-SOS (or first proposed technique). **EVALUATION:**

The two proposed plans and the ECC conspire introduced in [17] have been executed on a FPGA and assessed both

regarding overhead and mistake inclusion. A four-point annihilation in-recurrence FFT center is utilized to figure the FFT iteratively. This center has been created to MIMO-OFDM execute for remote frameworks. The usage of the four-point FFT center is appeared The quantity of FFT focuses is programmable and the turn coefficients are determined on-line for each stage and put away in registers. For the assessment, a 1024 FFT is designed with five phases figuring  $(\log 41024 = 5)$ , so altogether 5\*1024 = 5120 cycles are expected to figure the FFT for 1024 input tests. The information sources are 12-piece wide and the yields are 14-piece wide. For the excess FFT, the bit widths are stretched out to 14 and 16 piece, separately, to cover the bigger unique extend (as the data sources are the aggregate of a few signals). Since both the sources of info and yields to the FFT are consecutive, the SOS check is likewise done consecutively utilizing collectors that are analyzed toward the finish of the square. This is appeared in Fig. 5. To limit the effect of roundoffs on the flaw inclusion, the yields of the collector are 39piece wide. For the assessment, a few estimations of the quantity of parallel FFTs are considered. This is done to think about the various systems as a component of the quantity of parallel FFTs in the first framework. The blunder identification and remedy squares actualized are as multiplexers that select the right yield depending the blunder design on distinguished. As referenced previously, these squares are significantly increased to guarantee that blunders that influence them don't degenerate the last yields. The FFT

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

and the distinctive insurance systems have been actualized utilizing Verilog. At that point, the plan has been mapped to a Virtex-4 xc4vlx80 FPGA setting the greatest exertion on limiting the utilization of assets. The outcomes acquired are condensed in Tables III-VII. The first table gives the assets expected to execute a solitary FFT what's more, a SOS check. The outcomes show that the FFT is increasingly intricate than the SOS check true to form. The distinction will be a lot bigger at the point when a completely parallel FFT usage is utilized. Tables IV-VII show the outcomes when diverse number of parallel FFTs are secured. The goal is to represent how the family member overheads of the various strategies shift with the quantity of parallel FFTs. In brackets, the cost comparative with an unprotected usage is additionally given. The outcomes show that all strategies have a cost factor of <2. This shows the ECC-based strategy proposed in [17] is additionally aggressive to ensure FFTs what's more, requires a much lower cost than TMR. The equality SOS-ECC method has the most minimal asset use in all cases and, in this way, is the best choice to limit the usage cost. This is anticipated from the talk in Section II and the underlying appraisals exhibited in Table II. Then again, the equality SOS conspire needs less assets than the ECC plot when the quantity of FFTs is 4, 6, or 8 however more when the quantity of FFTs is 11. This can be clarified as in the ECC conspire, the quantity of extra FFTs develops logarithmically with the quantity of FFTs, while in the equality SOS procedure, the quantity of SOS checks develops directly. This implies as the quantity of FFTs to ensure builds, the ECC conspire turns out to be increasingly focused. For the equality SOS-ECC conspire, the quantity of SOS checks likewise develops logarithmically and they are more straightforward to execute than FFTs.

### CONCLUSION

In this short, the assurance of parallel FFTs execution against delicate mistakes has been contemplated. Two procedures have been proposed furthermore, assessed. The proposed methods depend on consolidating an existing ECC approach with the customary SOS check. The SOS checks are utilized to distinguish and find the blunders and a straightforward equality FFT is utilized for amendment. The recognition and area of the blunders should be possible utilizing a SOS check for each FFT or then again utilizing a set of SOS watches that structure an ECC. The proposed methods have been assessed both in wording of execution multifaceted nature and blunder location capacities. The outcomes show that the subsequent method, which utilizes an equality FFT and a lot of SOS watches that structure an ECC, gives the best brings about terms of usage multifaceted nature. As far as blunder assurance, deficiency infusion tests show that the ECC plot can recuperate every one of the mistakes that are out of the resistance go. The shortcoming inclusion for the equality SOS conspires and the equality SOS-ECC plot is ~99.9% when the resilience level for SOS check is 1.

### REFERENCES

[1] N. Kanekawa, E. H. Ibe, T. Suga, and Y. Uematsu, Dependability in Electronic Systems: Mitigation of Hardware Failures,

A Peer Revieved Open Access International Journal

www.ijiemr.org

Soft Errors, and Electro-Magnetic Disturbances. New York, NY, USA: Springer-Verlag,

[2] R. Baumann, "Delicate mistakes in cutting edge PC frameworks," IEEE Des. Test Comput., vol. 22, no. 3, pp. 258–266, May/Jun. 2005.

[3] M. Nicolaidis, "Structure for delicate mistake alleviation," IEEE Trans. Gadget Mater. Rel., vol. 5, no. 3, pp. 405–418, Sep. 2005.

[4] A. L. N. Reddy and P. Banerjee, "Calculation based flaw identification for signal handling applications," IEEE Trans. Comput., vol. 39, no. 10, pp. 1304–1308, Oct. 1990.

[5] T. Hitana and A. K. Deb, "Spanning simultaneous and non-simultaneous blunder identification in FIR channels," in Proc. Norchip Conf., Nov. 2004, pp. 75–78.

[6] S. Pontarelli, G. C. Cardarilli, M. Re, and A. Salsano, "Thoroughly deficiency tolerant RNS based FIR channels," in Proc. fourteenth IEEE Int. On-Line Test Symp. (IOLTS), Jul. 2008, pp. 192–194.

[7] B. Shim and N. R. Shanbhag, "Vitality effective delicate blunder tolerant advanced signal handling," IEEE Trans. Very Large Scale Integr. (VLSI) Syst.vol. 14, no. 4, pp. 336–348, Apr. 2006.

[8] E. P. Kim and N. R. Shanbhag, "Delicate N-secluded excess," IEEE Trans. Comput., vol. 61, no. 3, pp. 323–336, Mar. 2012.

[9] J. Y. Jou and J. A. Abraham, "Flaw tolerant FFT systems," IEEE Trans. Comput., vol. 37, no. 5, pp. 548–561, May 1988.

[10] S.- J. Wang and N. K. Jha, "Calculation based adaptation to non-critical failure for FFT systems," IEEE Trans. Comput., vol. 43, no. 7, pp. 849–854, Jul. 1994.[11] P. P. Vaidyanathanm, Multirate Systems and Filter Banks. Englewood

Cliffs, NJ, USA: Prentice-Hall, 1993.

[12] A. Sibille, C. Oestges, and A. Zanella, MIMO: From Theory to Execution. San Francisco, CA, USA: Academic, 2010.

[13] G. L. Stüber, J. R. Barry, S. W. McLaughlin, Y. Li, M. A. Ingram, and T. G. Pratt, "Broadband MIMO-OFDM remote correspondences," Proc. IEEE, vol. 92, no. 2, pp. 271–294, Feb. 2004.

[14] S. Sesia, I. Toufik, and M. Cook, LTE—The UMTS Long Term Evolution: From Theory to Practice, second ed. New York, NY, USA: Wiley, Jul. 2011.

[15] M. Ergen, Mobile Broadband— Including WiMAX and LTE. New York, NY, USA: Springer-Verlag, 2009.

16] P. Reviriego, S. Pontarelli, C. J. Bleakley, and J. A. Maestro, "Zone productive simultaneous blunder recognition and revision for parallel channels," IET Electron. Lett., vol. 48, no. 20, pp. 1258–1260, Sep. 2012.

[17] Z. Gao et al., "Deficiency tolerant parallel channels dependent on blunder revision codes," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 23, no. 2, pp. 384–387, Feb. 2015.

[18] R. W. Hamming, "Mistake distinguishing and blunder remedying codes," Bell Syst. Tech. J., vol. 29, no. 2, pp. 147–160, Apr. 1950.

[19] P. Reviriego, C. J. Bleakley, and J. A. Maestro, "A tale simultaneous mistake recognition strategy for the quick Fourier change," in Proc. ISSC, Maynooth, Ireland, Jun. 2012, pp. 1–5.

<sup>2010.</sup>

A Peer Revieved Open Access International Journal

www.ijiemr.org

Guide Details:

CH.KUTUMBA RAO, Assis. Professor the Department of ECE, in Sree Vahini Institute of Science & Technology. Student Details: K.PRADEEP, M.Tech in Sree Vahini Institute of Science &Technology.