PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

# COPY RIGHT

**2023 IJIEMR**. Personal use of this material is permitted. Permission from IJIEMR must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 10<sup>th</sup> Apr 2023. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-12&issue=Issue 04

# 10.48047/IJIEMR/V12/ISSUE 04/64

Title MULTILEVEL INVERTER WITH LOWER SWITCH COUNT

Volume 12, ISSUE 04, Pages: 532-538

Paper Authors Mr. Ch. Rambabu, E. Sruthi, B. Geetanjali, A. Srikanth, B. Madhu Harika

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

### **Multilevel Inverter with Lower Switch Count**

**Mr. Ch. Rambabu**<sup>1</sup>, Professor, Department of EEE, Vasireddy Venkatadri Institute of Technology, Nambur, Guntur Dt., Andhra Pradesh.

E. Sruthi<sup>2</sup>, B. Geetanjali<sup>3</sup>, A. Srikanth<sup>4</sup>, B. Madhu Harika<sup>5</sup> <sup>2,3,4,5</sup> UG Students, Department of EEE, Vasireddy Venkatadri Institute of Technology, Nambur, Guntur Dt., Andhra Pradesh. <sup>1</sup> rams\_babu2001@yahoo.com, 19bq1a0243@vvit.net, 19bq1a0220@vvit.net, 19bq1a0202@vvit.net, 19bq1a0222@vvit.net

### Abstract

Industrial drives use multilevel inverters (MLI) in a variety of ways. MLI applications in industrial drives have multiplied dramatically over the past 20 years. But, for more efficiency and dependability, we always require fewer devices. A Multilevel Inverter (MLI) output voltage can be adjusted using several modulation techniques. Intensive study is underway to reduce the number of DC power supplies and switches used in Multilevel Inverter without minimize the number of output levels. To increase the power handling capacity without purchasing new converters, MLI's modular design is implemented. This project demonstrates a cascaded H-bridge (CHB) converter with a decreased switch count that generates a seven-level output from a single stiff DC source (battery). To get a better output voltage waveform, gate pulses for the switches have been generated using the nearest level control (NLC) pulse-width modulation technology. The provided mathematical analysis is supported by simulation and experimental findings. The fluctuation of total harmonic distortion (THD) with modulation index is also investigated.

**Keywords:** Cascaded H-bridge (CHB) converter, MATLAB, Nearest level control (NLC), Total harmonic distortion (THD), Multilevel Inverter (MLI).

#### 1. Introduction

In 1981, the concept of a multilevel inverter was proposed [1,2]. Using a variety of DC voltage sources, these converters provide a sinusoidal-looking stepped output voltage [2-4]. Because the output of inverters has less harmonic distortion, they are frequently employed in industrial applications. In industrial applications, it is commonly used. The application field includes static VAR generation, the flexible AC transmission (FACTS), system solar photovoltaic systems [6, 7], and rechargeable batteries [8]. As a rectifier in the car for regenerative braking, MLI is also employed in traction drive [9]. The use of several switches and DC sources in multilevel inverters has increased the complexity of the circuitry, setting new possibilities for research to minimize it. The number of DC sources and switches

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

used in MLI is being minimized without affecting the number of output levels [10, 11]. The research project may be effectively split into two parts: developing appropriate control algorithms and discovering fresh topologies for attaining the previously mentioned purpose. Diode clamped, flying capacitor, and cascaded multilevel converters are the three categories for conventional multilevel converters. Cascaded multilevel converters are said to provide a simple, dependable, and modular structure. Asymmetrical CHB converter and symmetrical CHB converter are additional categories for converters cascading multilevel [12]. Asymmetrical CHB converters employ sources of DC voltage which are not equivalent to those used by symmetrical CHB converters. In compared to the various control approaches described in [13-16], overall least THD is produced with a simpler control.

An eight-switch cascaded H-bridge asymmetrical multilevel inverter with seven levels is investigated in this work. Increasing the level count improves the shape of the output waveform [17]. Multilevel inverter modulation control often uses both space vector PWM technologies and conventional PWM control techniques. The downside of the old PWM systems is the power waste in the switches owing to the high switching frequency. For motor driving applications, low switching frequency control techniques like the fundamental frequency approach and the concept of active harmonic removal has been proposed. A simulation model for the proposed seven-level CHB converter is constructed in the MATLAB®/Simulink environment. The study also includes results on the converter's performance.

### 2. Working of Multilevel Cascaded H-Bridge Inverter

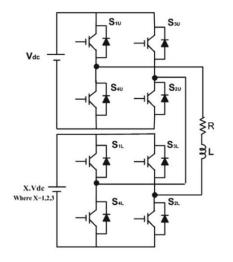

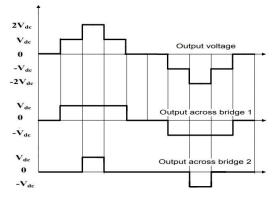

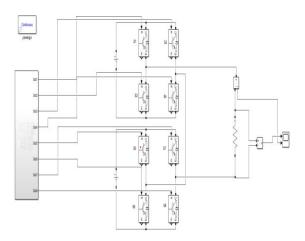

With (n - 1) / 2 DC sources and 2(n-1)switches can generate n-level output in a cascaded H-bridge inverter. Hence, three DC sources are needed to provide 7-level output with 12 switches, The switch count will be significantly reduced by asymmetric-cascaded CHB, though at the cost of a reduction in redundant states. Also, irrespective of the modulation approach, the output voltage will be asymmetric. Yet, the financial advantages of fewer switches and DC voltage sources are crucial in these kinds of inverter configurations for their use. The circuit design for two cascaded H-bridge converters is shown in Figure 1.The switching strategy for various output levels that might be produced by an asymmetric-cascaded CHB with various DC source combinations is shown in Fig 2. Using a battery voltage combination of Vdc and 2Vdc, a seven-level output might be produced.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### www.ijiemr.org

Figure 1: Two Cascaded H-Bridge Converters

### **3. Nearest Level Control**

The performance of a standard NLC degrades for a small count of levels, and the THD in the resultant voltage is considerable. Modified NLC is implemented in a modular multilevel converter suggested in [18] using model predictive control. To control and reduce the variations in a 4 level MLI of capacitor voltage, a control mechanism based on SPWM is utilized in [19]. While being easy to implement, the THD produced with the SPWM is high by IEEE standards at 24.7% [19]. A stepped voltage waveform a cascaded multilevel for inverter structure is produced in [20] using a phase-shifted PWM modulation approach. An enhanced NLC approach for MLI is put out in [21], and it is discovered that for a given number of submodules, the number of levels grows, lowering the THD in the resultant voltage. For grid-connected inverters, writers in [22] propose a hybrid PWM/Pulse Amplitude Modulation strategy. The converter's efficiency is raised by the suggested hybrid modulation approach. In [23], 15-levels are produced using the NLC switching approach.

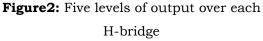

# 4. Execution of the Suggested CHB Strategy

Fig. 1 shows the cascaded h-bridge (CHB) inverter's generalized circuit configuration. One dc supply and four switches are included in one h-bridge device. Using two H-bridge units, the suggested NLM approach is applied on the seven-level CHB inverters. DC sources have magnitudes of V1 = V and V2 = 2V.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

**Figure3:** Figure shows how a n level CHBMLI is implemented using the NLC scheme.

### 5. Modulation and Switching Control

Equations provide the set of equations needed to perform the NLM system.

$$3msin(a1) = g ----(1)$$

3msin(a2) = 1 + g-----(2)

3msin(a3) = 2 + g ----(3)

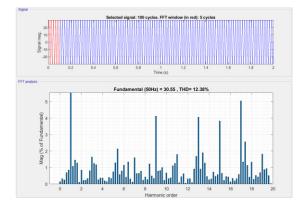

The switching angles in this case are ai(i = 1, 2, and 3), and g is the variable DC level of the VSNLM. The range of values is 0 to 1. The THD formula in eq. (A) was computed for harmonics up to 49 using data from [29]. By minimizing the THD expression provided in eq, one might determine g for a given value of the modulation index m. (A). As a result, appropriate values of g are found for minimal THD for all values of m between (0, 1). Equations (4) and (5) yield the set of (m, g) points, which may be used to determine the connection between m and g (Fig (5).

g = 1.37m - 0.87 for (m > 2/3) ---- (4) g = 1.38m - 0.42 for (1/3 < m < 2/3) ---(5)

$$\text{THD}_{7L} = \sqrt{\left(\frac{\pi^2}{8}\right)} \cdot \frac{9V_{dc}^2 - \frac{2}{\pi} \left[\alpha_1 V_{dc}^2 + 3\alpha_2 V_{dc}^2 + 5\alpha_3 V_{dc}^2\right]}{\left(V_{dc} \cos\alpha_1 + V_{dc} \cos\alpha_2 + V_{dc} \cos\alpha_3\right)^2} - 1$$

### 6. Multilevel Output Generation Using Cascaded H-Bridge Converter

By cascading two or more H-bridge converters, multilevel output can be produced. In principle, cascaded converters employing an equal-number DC source might provide the (2n + 1) level. By selecting an inequitable DC source, the level count rises. Two cascaded H-bridge converters are shown in Figure 1. Tables 1 illustrate the switching strategy for creating multiple multilayer outputs from two cascaded H-bridge converters with different DC voltage levels.

### **6.1 Five-Level Output**

The switching scheme for generating fivelevel output

| S <sub>1U</sub> | S <sub>2U</sub> | S3U | S4U | V1               | S <sub>1L</sub> | S <sub>2L</sub> | S3L | S <sub>4L</sub> | V2               | Vo                |

|-----------------|-----------------|-----|-----|------------------|-----------------|-----------------|-----|-----------------|------------------|-------------------|

| On              | On              | -   | -   | V <sub>dc</sub>  | On              | On              | -   |                 | Vác              | 2Vdc              |

| On              | On              | -   |     | Vdc              | On              | -               | -   | -               | 0                | Vdc               |

| -               |                 |     |     | 0                | -               | -               | -   |                 | 0                | 0                 |

| -               |                 | On  | On  | -V <sub>dc</sub> | -               | On              | -   | On              | -                | -V <sub>dc</sub>  |

| -               |                 | On  | On  | -V <sub>dc</sub> | -               | -               | On  | On              | -V <sub>dc</sub> | -2V <sub>dc</sub> |

Table1: Five Level Switching Scheme

# 7. Simulation and Experimental Results

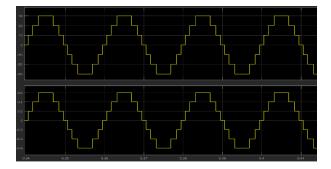

The sine block included in the SIMULINK library browser is used to create the sine wave. The frequency of sine wave is taken 50 Hz. Modulation value (m) is taken as 1 because for less than m=0.8, levels will reduce so we consider m=1. Bv mathematical equations g value will be 0.5(g=0.5). Generate pulses by pulse generator block. Eliminate negative wave forms in positive signal vice versa by multiplying pulse to positive and negative signals. Resultant signals are combined

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

and injected to Cascaded H-Bridge circuit and voltages of dc sources are 1:2 ratio and switching scheme is as shown in table (2).

| Levels | <b>S1</b> | S2  | <b>S</b> 3 | <b>S</b> 4 | S5  | S6  | S7  | <b>S8</b> | VRL |

|--------|-----------|-----|------------|------------|-----|-----|-----|-----------|-----|

| 1      | ON        | OFF | OFF        | ON         | OFF | ON  | OFF | ON        | ۷   |

| 2      | OFF       | ON  | OFF        | ON         | ON  | OFF | OFF | ON        | 2V  |

| 3      | ON        | OFF | OFF        | ON         | ON  | OFF | OFF | ON        | 3V  |

| 4      | OFF       | ON  | OFF        | ON         | OFF | ON  | OFF | ON        | 0   |

| 5      | OFF       | ON  | ON         | OFF        | OFF | ON  | OFF | ON        | -V  |

| 6      | OFF       | ON  | OFF        | ON         | OFF | ON  | ON  | OFF       | -2V |

| 7      | OFF       | ON  | ON         | OFF        | OFF | ON  | ON  | OFF       | -3V |

Table2: Seven Level Switching Scheme

**Figure4:** Simulation Diagram for Seven level Cascaded MLI with Reduced Switch Count.

Figure5: Simulation Results

Figure6: THD Analysis

### 8. Conclusion

This study looked at a different method for generating a cascaded H-bridge multilevel inverter's seven-level output with few switches and sources. A Nearest Level Control (NLC) technique was successfully used to reduce the THD of the output voltage. The outcomes of the experiments have verified the technique.

### 9. References:

[1]. Nabae, A., Takahashi, I., & Akagi, H.

(1981). A new neutral-point-clamped

PWM inverter. *IEEE Transactions on industry applications*, (5), 518-523.

[2]. Tariq, A., Husain, M. A., Ahmad, M., & Tariq, M. (2011, May). Simulation and study of a grid connected multilevel converter (MLC) with varying DC input. In 2011 10th International Conference on Environment and Electrical Engineering (pp. 1-4). IEEE.

[3]. Lai, J. S., & Peng, F. Z. (1996). Multilevel converters-a new breed of power converters. *IEEE Transactions on industry applications*, *32*(3), 509-517.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

[4]. Bharatiraja, C., Munda, J. L., Bavindir, R., & Tariq, Μ. (2016,November). А common-mode leakage current mitigation for PV-grid connected three-phase three-level transformerless Ttype-NPC-MLI. In 2016 IEEE International Conference on Renewable Energy Research and Applications (ICRERA) (pp. 578-583). IEEE.

[5]. Rathore, S., Kirar, M. K., & Bhardwaj, S. K. (2015). Simulation of cascaded H-bridge multilevel inverter using PD, POD, APOD techniques. *Electrical & Computer Engineering: An International Journal (ECIJ), 4*(3), 27-41.

[6]. Sarwar, A., & Asghar, M. J. (2010, December). Multilevel converter topology for solar PV based grid-tie inverters.

In 2010 IEEE International Energy Conference (pp. 501-506). IEEE.

[7]. Tariq, M., Bhardwaj, S., & Rashid, M. (2013). Effective battery charging system by solar energy using C programming and microcontroller. *American Journal of Electrical Power and Energy Systems*, 2(2), 41-43.

[8]. Rodriguez-Rodríguez, J. R., Venegas-Rebollar, V., & Moreno-Goytia, E. L. (2015). Single DC-sourced 9-level DC/AC topology as transformerless power interface for renewable sources. *Energies*, 8(2), 1273-1290.

[9]. Du, Z., Ozpineci, B., Tolbert, L. M., & Chiasson, J. N. (2009). DC–AC cascaded H-bridge multilevel boost inverter with no inductors for electric/hybrid electric vehicle applications. *IEEE Transactions on Industry Applications*, 45(3), 963-970.

[10]. Tariq, M., Iqbal, M. T., Meraj, M., Iqbal, A., Maswood, A. I., & Bharatiraja, C. (2016, December). Design of a proportional resonant controller for packed U cell 5 level inverter for gridconnected applications. In 2016 IEEE International Conference on power electronics, drives and energy systems (PEDES) (pp. 1-6). IEEE.

[11]. Tariq, M., Iqbal, M. T., Iqbal, A., Meraj, M., Roomi, M. M., & Khan, M. S. U. (2016, January). Comparative analysis of carrier schemes for PWM in multilevel PUC inverter for PV applications. In 2016 4th International Conference on the Development in the in Renewable Energy Technology (ICDRET) (pp. 1-6). IEEE.

[12]. Wu, B., & Narimani, M.(2017). *High-power converters and AC drives*. John Wiley & Sons.

[13]. Kavitha M, Arunkumar A, Gokulnath N, Arun S (2013) New cascaded multilevel inverter topology with reduced number of switches and sources. In: 2013 8th international conference on electrical and electronics engineering (ELECO), vol 2, no 6, pp 97–101

[14]. Kumar, P. S., Natarajan, D. S., Nachiappan, A., & Shanthi, B. (2013). Performance evaluation of nine level modified CHB multilevel inverter for various PWM strategies. *International Journal of Modern Engineering Research (IJMER)*, *3*(5), 2758-2766.

[15]. Murali Krishna T (2015) Matlab Simulink modeling of hybrid cascaded five

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

level inverters. Int J Sci Res 4(12):834– 837

[16]. Kumar, V., Mittal, A., & Saifee, A. H.

(2014). A new model of H-bridge multilevel inverter for reduced harmonics distortion. International Journal of Engineering Research and Applications, 4(11), 30-35.

[17]. Tariq, M., & Iqbal, M. T. (2014). Power quality improvement by using multi-pulse AC-DC converters for DC drives: Modeling, simulation and its digital implementation. *Journal of Electrical Systems and Information Technology*, 1(3), 255-265.

[18]. Yin, J., Leon, J. I., Perez, M. A., Franquelo, L. G., Marquez, A., Li, B., & Vazquez, S. (2020). Variable rounding level control method for modular multilevel converters. *IEEE Transactions on Power Electronics*, *36*(4), 4791-4801.

[19]. Bahrami, A., & Narimani, M. (2018). A sinusoidal pulsewidth modulation (SPWM) technique for capacitor voltage balancing of a nested T-type four-level inverter. *IEEE transactions on Power Electronics*, 34(2), 1008-1012.

[20]. Sun, D., Ge, B., Peng, F. Z.,

Haitham, A. R., Bi, D., & Liu, Y. (2012,

May). A new grid-connected PV system

based on cascaded H-bridge quasi-Z

source inverter. In 2012 IEEE

International Symposium on Industrial

Electronics (pp. 951-956). IEEE.

[21]. Hu, P., & Jiang, D. (2014). A levelincreased nearest level modulation method for modular multilevel converters. *IEEE transactions on Power Electronics*, *30*(4), 1836-1842.

[22]. Liu, Y., Ge, B., Abu-Rub, H., & Sun,

H. (2016). Hybrid pulsewidth modulated

single-phase quasi-Z-source grid-tie

photovoltaic power system. *IEEE*transactions on Industrial

Informatics, 12(2), 621-632.

[23]. Ceglia, G., Grau, V., Guzman, V., Sanchez, C., Ibanez, F., Walter, J., ... & Gimenez, M. I. (2004, November). A new multilevel inverter topology. In Proceedings Fifth IEEE of the International Caracas Conference on Devices, Circuits and Systems, 2004. (Vol. 1, pp. 212-218). IEEE.