A Peer Revieved Open Access International Journal

www.ijiemr.org

## COPY RIGHT

**2017 IJIEMR**. Personal use of this material is permitted. Permission from IJIEMR must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 20 May 2017. Link :

http://www.ijiemr.org/downloads.php?vol=Volume-6&issue=ISSUE-3

Title: Implementation Of Qca Binary Adders Using Verilog Hdl.

Volume 06, Issue 03, Pages: 246 – 255.

Paper Authors

#### CHANDU DEVI, CH.NAVYA DEEPTHI.

Dept of ECE Sri Sunflower College of Engineering and Technology.

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

## IMPLEMENTATION OF QCA BINARY ADDERS USING VERILOG HDL

### \*CHANDU DEVI, \*\*CH.NAVYA DEEPTHI

\*PG Scholar, Dept of ECE (VLSID), Sri Sunflower College of Engineering and Technology, Lankapalli , (A.P),India. \*\*Assistant Professor, Department of ECE, Sri Sunflower College of Engineering and Technology, Lankapalli , (A.P),India

Email ID: <a href="mailto:chandudevi95@gmail.com">chandudevi95@gmail.com</a>, <a href="mailto:navyabushn@gmail.com">navyabushn@gmail.com</a>,

#### **ABSTRACT:**

As transistors decrease in size more and more of them can be accommodated in a single die, thus increasing chip computational capabilities. However, transistors cannot get much smaller than their current size. The quantum-dot cellular automata (QCA) approach represents one of the possible solutions in overcoming this physical limit, even though the design of logic modules in QCA is not always straightforward. In this brief, we propose a new adder that outperforms all state-of-the-art competitors and achieves the best area-delay tradeoff. The above advantages are obtained by using an overall area similar to the cheaper designs known in literature. The 16-bit, 32-bit and 64-bit version of the novel adder is implemented by verilog language and simulated using xilinix ISE9.1.

Keywords: Adders, nanocomputing, quantum-dot cellularautomata (QCA).

## **I INTRODUCTION**

In electronics, an adder or summer is a digital circuit that performs addition of numbers. In many computers and other kinds of processors, adders are used not only in the arithmetic logic unit(s), but also in other parts of the processor, where they are used to calculate addresses, table indices, and similar operations. Although adders can be constructed for many numerical representations, such as binary-coded decimal or excess-3, the most common adders operate on binary numbers. In cases where two's complement or ones' complement is being used to represent negative numbers, it is trivial to

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

modify an adder into an adder-subtractor. Other signed number representations require a more complex adder.Quantum-dot cellular automata (QCA) is an attractive emerging technology suitable for the development of ultradense lowpower high-performance digital circuits [1]. For this reason, in the last few years, the design of efficient logic circuits in QCA has received a great deal of attention. Special efforts are directed to arithmetic circuits [2]–[7], with the main interest focused on the binary addition that is the basic operation of any digital system. Of course, the architectures commonly employed in traditional CMOS designs are considered a first reference for the new design environment. Ripple-carry (RCA), carry look-ahead (CLA), and conditional sum adders were presented. The carry-flow adder (CFA) shown in was mainly an improved RCA in which detrimental wires effects were mitigated. Parallel-prefix architectures, including Brent-Kung (BKA), Kogge-Stone, adner-Fischer, and Han-Carlson adders, were analyzed and implemented in QCA. Recently, more efficient designs were proposed for the CLA and the BKA, and in [for the CLA and the CFA. In this brief, an innovative technique is presented to implement high-speed low-area adders in QCA. Theoretical formulations demonstrated in for

CLA and parallel-prefix adders are here exploited for the realization of a novel 2-bit addition slice. The latter allows the carry to be propagated through two subsequent bitpositions with the delay of just one majority gate (MG). In addition, the clever top level architecture leads to very compact layouts, thus avoiding unnecessary clock phases due to long interconnections.An adder designed as proposed runs in the RCA fashion, but it exhibits a computational delay lower than all state-of the art competitors and achieves the lowest areadelay product (ADP).

## **II.LITERATURE SURVEY**

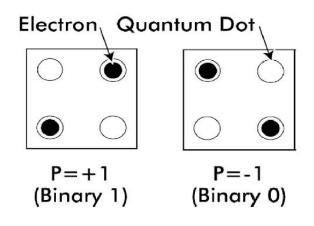

A QCA is a nanostructure having as its basic cell a square four quantum dots structure charged with two free electrons able to tunnel through the dots within the cell [1]. Because of Coulombic repulsion, the two electrons will always reside in opposite corners. The locations of the electrons in the cell (also named polarizations P) determine two possible stable states that can be associated to the binary states 1 and 0.Quantum - dot cellular automata (QCA) are an attractive emerging technology suitable for the development of ultra dense low-power high-performance digital circuits. For this reason, in the last few years, the design of efficient logic circuits in QCA has received a great deal of attention. Special efforts are directed to arithmetic circuits,

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

with the main interest focused on the binary addition that is the basic operation of any digital system. Of course, the architectures commonly employed in traditional CMOS designs are considered a first reference for the new design environment. Ripplecarry (RCA), carry look-ahead (CLA), and conditional sum adders were presented in. The carry-flow adder (CFA) shown in was mainly an improved RCA in which detrimental wires effects mitigated. Parallel-prefix were architectures, including Brent-Kung (BKA), Kogge-Stone, Ladner-Fischer, and Han-Carlson adders, were analyzed and implemented in QCA in and. Recently, more efficient designs were proposed in for the CLA and the BKA, and in for the CLA and the CFA. In this brief, an innovative technique is presented to implement high-speed low-area adders in QCA. Theoretical formulations demonstrated in for CLA and parallel -prefix adders are here exploited for the realization of a novel 2-bit addition slice. The latter allows the carry to be propagated through two subsequent bit-positions with the delay of just one majority gate (MG). In addition, the clever top level architecture leads to very compact layouts, thus avoiding unnecessary clock phases due to long interconnections. An adder designed as proposed runs in the RCA fashion, but it exhibits a computational delay lower than all state-of the-art competitors and achieves the lowest area-delay product (ADP). In this brief, an innovative technique is presented to implement high-speed low-area adders in QCA. CLA and parallel-prefix adders are

here exploited for the realization of a novel 2-bit addition slice. The latter allows the carry to be propagated through two subsequent bit-positions with the delay of just one majority gate (MG). In addition, the clever top level architecture leads to very compact layouts, thus avoiding unnecessary clock phases due to long interconnections. An adder designed as proposed runs in the RCA fashion,but it exhibits a computational delay lower than all stateof the-art competitors and achieves the lowest areadelay product (ADP).

## **III. PROBLEM OUTLINE**

#### **EXISTING SYSTEM**

The Existing adder design follows that of a conventional ripple carry adder, but with a new layout optimized to QCA technology. The proposed adder design shows that a very high delay can be obtained with an optimized layout. This is in contrast to the conventional ripple carry adder. To avoid confusion, the new layout is referred to as the Carry Flow Adder (CFA) here. In this Carry Flow Adder occupy more Number of gate Counts and More Delay.

#### **EXISTING SYSTEM TECHNIQUE:**

• QCA Design Scheme

#### **EXISTING SYSTEM DRAWBACKS:**

Compare to proposed system

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

- Low operation speed and more Delay

- Adders can be implemented in larger Area

#### **PROPOSED SYSTEM:**

An innovative technique is presented to implement high-speed low-area adders in QCA. The CLA and parallel-prefix adders are here exploited for the realization of a novel 2-bit addition slice. The latter allows the carry to be propagated through two subsequent bit-positions with the delay of just one majority gate (MG). In addition, the clever top level architecture leads to very compact layouts, thus avoiding unnecessary clock phases due to long interconnections.

#### **PROPOSED SYSTEM TECHNIQUE:**

• QCA Design Based Majority gate

#### **PROPOSED SYSTEM ADVANTAGES:**

- Area Efficient

- Delay Efficient

## IV. METHODOLOGY

#### **Majority QCA:**

The fundamental logic gates inherently available within the QCA technology are the inverter and the MG. Given three inputs a, b, and c, the MG performs the logic function

reported in equation (1) provided that all input cells are associated to the same clock signal clkx, whereas the remaining cells of the MG are associated to the clock signal clkx+1.

$$M(abc) = a \cdot b + a \cdot c + b \cdot c. \quad \dots \quad (1)$$

In this project, a novel quantum-dot cellular automata (QCA) adder design is presented that decrease the number of QCA cells. The proposed one-bit QCA adder design is based on a new algorithm that requires only three majority gates and two inverters for the QCA addition. A novel 64-bit adder designed in QCA implemented. It achieved speed was performances higher than all the existing. QCA adders, with an area requirement comparable with the cheap RCA and CFA established. The novel adder operates in the RCA fashion, but it could propagate a carry signal through a number of cascaded MGs significantly lower than conventional RCA adders. In adding together, because of the adopted basic logic and layout strategy, the number of clock cycles required for completing the explanation was limited. As transistors reduce in size more and more of them can be accommodated in a single die, thus increasing chip computational capabilities. However, transistors cannot find much smaller than their current size. The quantum-dot cellular

Volume 06, Issue 03, May 2017.

A Peer Revieved Open Access International Journal

#### www.ijiemr.org

automata approach represents one of the possible solutions in overcome this physical limit, even though the design of logic modules in QCA is not forever straightforward.

A quantum-dot cellular automaton (QCA) is an attractive emerging technology suitable for the development of ultra dense low-power higherperformance digital circuits. For this cause in the last few years, the design of proficient logic circuits in QCA has received a great deal of attention. Special efforts are directed to arithmetic circuits, with the major interest focused on the binary addition that is the basic operation of any digital system. Of course, the designs commonly employed in traditional CMOS designs are considered a first reference for the new design environment. Ripple-carry, carry look-ahead (CLA), and conditional sum adders were implemented in. The carry-flow adder shown in was mainly an improved RCA in which detrimental wires effects were mitigated. Parallel-prefix architectures, including Brent-Kung (BKA), Kogge-Stone, Ladner-Fischer, and Han-Carlson adders, were analyzed and implemented in QCA. Recently, further efficient designs were proposed for the CLA and the BKA, and for the CLA and the CFA. In this brief, an innovative technique is presented to implement high-speed low-area

adders into QCA. Theoretical formulations established for CLA and parallel-prefix adders are here exploited for the realization of a novel 2-bit addition slice. The latter allows the carry to be propagated through two subsequent bitpositions with the delay of just one majority gate (MG). In addition, the clever top level architecture leads to very compact layouts, thus avoiding unnecessary clock phases due to lengthy interconnections.

The prefix operation has three stages:

- 1. Pre calculation of pi,gi in each stage.

- 2. Calculation of carry ci for each stage.

3. Combine ci,pi to generate the sum bit and the carry bit "Si" and Cout

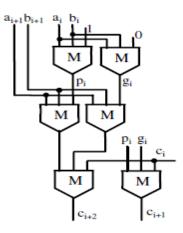

Fig 1: novel 2-bit basic module

Volume 06, Issue 03, May 2017.

A Peer Revieved Open Access International Journal

www.ijiemr.org

To introduce the novel design proposed for implementing ripple adders in QCA, let consider two *n*-bit addends A = an-1,...a0, and B = bn-1,....b0 and suppose that for the *i* th bit position (with i = n - 1, ..., 0) the auxiliary propagate and generate signals, namely pi=ai+bi and gi=ai.bi, are computed ci being the carry produced at the generic (*i*-1)th bit position, the carry signal *ci*+2, furnished at the (*i*+1)th bit location. an RCA adder designed as proposed has a worst case path almost halved with respect to the conventional RCA and CFA.

#### QCA Basics

QCA is based on the interface of bi-stable QCA cells constructed from four quantum-dots. A high-level design of two polarized QCA cells is shown in Fig. 2. Each cell is constructed from four quantum dots arranged in a square pattern. The cell is charged with two electrons, which are free of charge to tunnel between adjacent dots. These electrons tend To take up antipodal sites as a result of their mutual electrostatic Thus, there exist two repulsion. equal energetically minimal arrangements of the two electrons in the QCA cell as shown in Fig. 2. These two arrangements are denoted as cell polarization P = +1 and P = -1 correspondingly. By using cell polarization P = +1 to represent logic "1" and P = -1 to represent logic "0", binary information can be encoded.

#### Fig 2: QCA cells

Arrays of QCA cells can be set to perform all logic functions. This is owed to the Columbic interactions, which influences the polarization of neighboring cells. QCA designs have been proposed with potential barriers between the dots that can be controlled and used to clock QCA designs.

### **QCA Logical Devices:**

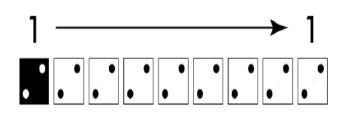

The fundamental QCA logic devices are the QCA wire, majority gate and inverter. **QCA wire**: In a QCA wire, the binary signal propagates from input to output because of the Columbic connections between cells. This is a result of the system attempting to settle to a ground state. Any cells along the wire that are anti-polarized to the input would be at a high

A Peer Revieved Open Access International Journal

energy level, and would soon settle to the correct ground state. The propagation in a 90degree QCA wire is shown in Figure. Other than the 90-degree QCA wire, a 45-dgree QCA wire can also be used. In this case, the propagation of the binary signal alternates between the two polarizations. Advance, there exists a so-called non-linear QCA wire, in which cells with 90-degree orientation can be placed next to one more, but off center.

#### Fig 3: AQCA wire (90-degrees)

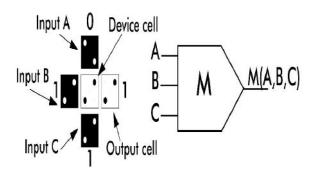

**Majority gate and inverter**: The majority gate and inverter are shown in below Figures respectively. The majority gate performs a three-input logic function. Assuming the inputs is A, B and C, the logic function of the majority gate is

### m(A, B, C) = A|B + B|C + A|C

By fixing the polarization of one input as logic "1" or "0", we can get an OR gate and an AND gate respectively. More complex logic circuits can then be designed from OR and AND gates.

www.ijiemr.org

Fig 4: A QCA majority gate

Fig 5: A QCA inverter

**V.RESULTS**

### SIMULATION RESULTS:

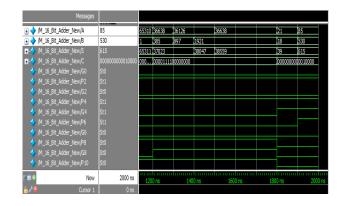

### 16-BIT QSD ADDER:

### Fig 6 : 16-Bit Qsd Adder

Volume 06, Issue 03, May 2017.

A Peer Revieved Open Access International Journal

www.ijiemr.org

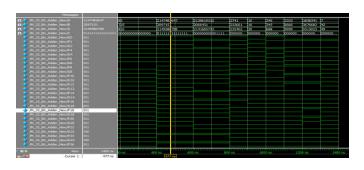

### **32-BIT QSD ADDER:**

Fig 7 : 32-Bit QSD Adder

#### 64-BIT QSD ADDER:

| Messages                  |                                                                                 |                                         |                     |           |        |          |     |

|---------------------------|---------------------------------------------------------------------------------|-----------------------------------------|---------------------|-----------|--------|----------|-----|

| + 🔷 /M_64_Bit_Adder_New/A | 500                                                                             | 1073741823                              | 48320974825434027   | 1280      | 500    |          |     |

| + 🔷 /M_64 Bit_Adder_New/B | 800                                                                             | 22905493530                             | 2541551403134113400 | 11280     | 300    |          |     |

| +                         | 1300                                                                            | 25980285353                             | 2589872377959547427 | 2560      | 1300   |          |     |

|                           | 000000000000000000000000000000000000000                                         | 000000000000000000000000000000000000000 |                     | . 000000. |        |          |     |

| M_64_Bit_Adder_New/GD     | SHD                                                                             |                                         |                     |           |        |          |     |

| /M_64_Bit_Adder_New/P2    |                                                                                 |                                         |                     |           |        |          |     |

| 👍 /M_64_Bit_Adder_New/G2  | 5t1<br>5t0                                                                      |                                         |                     |           |        |          |     |

| M_64_Bit_Adder_New/P4     |                                                                                 |                                         |                     |           |        |          |     |

| 4 M_64_Bit_Adder_New/G4   | St0                                                                             |                                         |                     |           |        |          |     |

| M_64_Bit_Adder_New/P6     | 511<br>510<br>511<br>510<br>511                                                 |                                         |                     |           |        |          |     |

| 1 M 64 Bit_Adder_New/G6   | St0                                                                             |                                         |                     |           |        |          |     |

| M_64_Bit_Adder_New/P8     |                                                                                 |                                         |                     |           |        |          |     |

| 👍 M_64_Bit_Adder_New/G8   |                                                                                 |                                         |                     |           |        |          |     |

| 🔶 /M_64_Bit_Adder_New/P10 | St1<br>St0                                                                      |                                         |                     |           |        |          |     |

| 👍 /M_64_Bit_Adder_New/G10 |                                                                                 |                                         |                     |           |        |          |     |

| /M_64_Bit_Adder_New/P12   | 560                                                                             |                                         |                     |           |        |          |     |

| 4 M 64 Bit Adder New/G12  | St0                                                                             |                                         |                     |           |        |          |     |

| M_64_Bit_Adder_New/P14    | 510                                                                             |                                         |                     |           |        |          |     |

| /M_64_Bit_Adder_New/G14   | 560                                                                             |                                         |                     |           |        |          |     |

| 4 M_64_Bit_Adder_New/P16  | 560                                                                             |                                         |                     |           |        |          |     |

| M_64_Bit_Adder_New/G16    | St0                                                                             |                                         |                     |           |        |          |     |

| /M_64_Bit_Adder_New/P18   | 560                                                                             |                                         |                     |           |        |          |     |

| /M_64_Bit_Adder_New/G18   | St0                                                                             |                                         |                     |           |        |          |     |

| /M_64_Bit_Adder_New/P20   | St0                                                                             |                                         |                     |           |        |          |     |

| /M_64_Bit_Adder_New/G20   | St0                                                                             |                                         |                     |           |        |          |     |

| /M_64_Bit_Adder_New/P22   | 50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>5 |                                         |                     |           |        |          |     |

| /M_64_Bit_Adder_New/G22   |                                                                                 |                                         |                     |           |        |          |     |

| M_64_Bit_Adder_New/P24    | 560                                                                             |                                         |                     |           |        |          |     |

| 4 M_64_Bit_Adder_New/G24  |                                                                                 |                                         |                     |           |        |          |     |

| M_64_Bit_Adder_New/P26    | StD                                                                             |                                         |                     |           |        |          |     |

| Now                       | 800 ns                                                                          | 200 ns                                  |                     | 00 ns     | 800 ns | 1000 ns  | 120 |

| /a Curser 1               | Ons                                                                             | 200 //S                                 | 10015 0             | W16       | ouuns  | 1000 115 | 140 |

Fig 8 : 64-Bit Qsd Adder

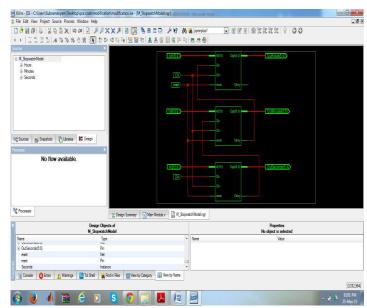

**MODIFICATION PART:**

**SYNTHESIS RESULTS:**

**RTL SCHEMATIC:**

#### **Fig 9: RTL SCHEMATIC**

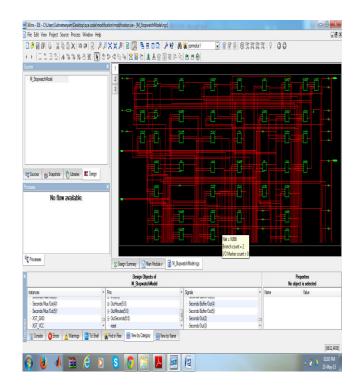

### **TECHNOLOGY SCHEMATIC:**

#### Fig 10: Technology Schematic

A Peer Revieved Open Access International Journal

www.ijiemr.org

### **DESIGN SUMMARY:**

| Device Utilization Summary                     |       |           |             |         |  |  |  |  |  |

|------------------------------------------------|-------|-----------|-------------|---------|--|--|--|--|--|

| Logic Utilization                              | Used  | Available | Utilization | Note(s) |  |  |  |  |  |

| Number of Slice Flip Flops                     | 16    | 7,168     | 1%          |         |  |  |  |  |  |

| Number of 4 input LUTs                         | 113   | 7,168     | 1%          |         |  |  |  |  |  |

| Logic Distribution                             |       |           |             |         |  |  |  |  |  |

| Number of occupied Slices                      | 61    | 3,584     | 1%          |         |  |  |  |  |  |

| Number of Slices containing only related logic | 61    | 61        | 100%        |         |  |  |  |  |  |

| Number of Slices containing unrelated logic    | 0     | 61        | 0%          |         |  |  |  |  |  |

| Total Number of 4 input LUTs                   | 113   | 7,168     | 1%          |         |  |  |  |  |  |

| Number of bonded <u>IOBs</u>                   | 39    | 141       | 27%         |         |  |  |  |  |  |

| Number of GCLKs                                | 1     | 8         | 12%         |         |  |  |  |  |  |

| Total equivalent gate count for design         | 830   |           |             |         |  |  |  |  |  |

| Additional JTAG gate count for IOBs            | 1,872 |           |             |         |  |  |  |  |  |

| Performance Summary   |                               |              |               |  |  |  |  |

|-----------------------|-------------------------------|--------------|---------------|--|--|--|--|

| Final Timing Score: 0 |                               | Pinout Data: | Pinout Report |  |  |  |  |

| Routing Results:      | All Signals Completely Routed | Clock Data:  | Clock Report  |  |  |  |  |

## Fig 11: Design Summary SIMULATION RESULT:

### Fig 12: Simulation Result

## **VI.CONCLUSION**

In this project, we have considered primitives in QCA and have presented an efficient QCA design for an *n*-bit ripple carry adder. The novel adder operated in the RCA fashion, but it could propagate a carry signal through a number of cascaded MGs significantly lower than conventional RCA adders. So, from the results we can observe that the QCA adder will occupy less area than the normal adders and also produce less delay when compared to the normal adder.

## **VII REFERENCES**

[1] C. S. Lent, P. D. Tougaw, W. Porod, and G.H. Bernestein, "Quantum cellular automata," *Nanotechnology*, vol. 4, no. 1, pp. 49–57, 1993.

[2] M. T. Niemer and P. M. Kogge, "Problems in designing with QCAs Layout = Timing," *Int. J. Circuit Theory Appl.*, vol. 29, no. 1,pp. 49– 62, 2001.

[3] J. Huang and F. Lombardi, *Design and Test* of Digital Circuits by Quantum-Dot Cellular Automata. Norwood, MA, USA: Artech House,2007.

A Peer Revieved Open Access International Journal

www.ijiemr.org

[4] W. Liu, L. Lu, M. O'Neill, and E. E. Swartzlander, Jr., "Design rules for quantum-dot cellular automata," in *Proc. IEEE Int. Symp. Circuits Syst.*, May 2011, pp. 2361–2364.

[5] K. Kim, K. Wu, and R. Karri, "Toward designing robust QCA architectures in the presence of sneak noise paths," in *Proc. IEEE Design, Autom. Test Eur. Conf. Exhibit.*, Mar. 2005, pp. 1214–1219.

## **VIII AUTHORS**

### **AUTHOR 2**

**CHANDHU DEVI,** ,PG scholar Dept of ECE (VLSID), Sri Sunflower College of Engineering and Technology, B.Tech degree in Electronics and Communication Engineering at Sri Sunflower College of Engineering and Technology.

**CH.NAVYA DEEPTHI** Working as assistant professor of ECE, Sri. Sunflower College of Engineering and Technology, Lankapalli. She received the M.Tech degree in Digital electronics and communication Engineering from Dr. Samuel George College of engineering and technology. Markapuram., B.Tech degree in Electronics and Communication Engineering at sindhura college of engineering and technology. Ramagundamand, she has total Teaching Experience (UG and PG) of 6 years.