A Peer Revieved Open Access International Journal

www.ijiemr.org

## **COPY RIGHT**

2017 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 11<sup>th</sup> June 2017. Link:

http://www.ijiemr.org/downloads.php?vol=Volume-6&issue=ISSUE-4

**Title**: High-Speed And Energy-Efficient Carry Skip Adder Operating Under A Wide Range Of Supply Voltage Levels.

Volume 06, Issue 04, Page No: 873 – 877.

**Paper Authors**

\*NARABOINA HARIKA, \*\*KUMMARIKUNTLA SHRAVANI.

\* Dept Of ECE Anurag Engineering College.

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# HIGH-SPEED AND ENERGY-EFFICIENT CARRY SKIP ADDER OPERATING UNDER A WIDE RANGE OF SUPPLY VOLTAGE LEVELS

\*NARABOINA HARIKA, \*\*KUMMARIKUNTLA SHRAVANI

\*Assistant Professor, Dept Of ECE(Embedded Systems), ANURAG ENGINEERING COLLEGE

\*\*PG Scholar, Dept Of ECE (VLSI-SD), ANURAG ENGINEERING COLLEGE

naraboinaharika@gmail.com sravs.gates555@gmail.com

ISSN: 2456 - 5083

### **ABSTRACT:**

In this paper, we present a carry skip adder(CSKA) structure that has a higher speed yet lower energy consumption compared with the convention alone. The speed enhancement is achieved by applying concatenation and incrementation schemes to improve the efficiency of the conventional CSKA (Conv-CSKA) structure. In addition, instead of utilizing multiplexer logic, the proposed structure makes use of AND-OR Invert (AOI) and OR-AND-Invert (OAI) compound gates for the skip logic. The structure may be realized with both fixed stage size and variable stage size styles, where in the latter further improves the speed and energy parameters of the adder. Finally, a hybrid variable latency extension of the proposed structure, which lowers the power consumption without considerably impacting the speed, is presented. This extension utilizes a modified parallel structure for increasing the slacktime, and hence, enabling further voltage reduction. The proposed structures are assessed by comparing their speed, power, and energy parameters with those of other addersusing a 45nm static CMOS technology for a wide range of supply voltages. The results that are obtained using HSPICE simulations reveal, on average, 44% and 38% improvements in the delay and energy, respectively , compared with those of the Conv-CSKA. In addition, the power-delay product was the lowest among the structures

considered in this paper, while its energy—delay product was almost the same as that of the Kogge—Stone parallel prefix adder with considerably smaller area and power consumption. Simulations on the proposed hybrid variable latency CSKA reveal reduction in the power consumption compared with the latest works in this field while having a reasonably high speed.

**KEYWORDS**: Carry skip adder(CSKA),energy efficient, high performance, hybrid variable latency adders, voltage scaling

### I. INTRODUCTION

There are many works on the subject of optimizing the speed and power of these units, which have been reported in [2]-[9]. Obviously, it is highly desirable to achieve higher speeds at low-power / energy consumptions, which is a challenge for the designers of general purpose processors. One of the effective techniques to lower the power consumption of digital circuits is to reduce the supply voltage due to quadratic dependence of the switching energy on the voltage. Moreover, the sub threshold current, which is the main leakage component tin OFF devices, has an exponential dependence on the supply voltage level through the drain-induced barrier lowering effect[10]. Depending on the amount of the supply voltage reduction, the

A Peer Revieved Open Access International Journal

www.ijiemr.org

operation of ON devices may reside in the super threshold, near-threshold, or threshold regions. Working in the super threshold region provides us with lower delay and higher switching and leakage powers compared with the near/sub threshold regions. In the sub threshold region, the logic gate delay and leakage power exhibit exponential dependences on the supply and threshold Moreover. voltages. these voltages are(potentially)subject to process and environmental variations in the nano scale technologies. Thevariations increase uncertainties in the a fore said performance parameters. In addition, the small sub threshold current causes a large delay for the circuits operating in the sub threshold region[10]. Recently, the near-threshold region has been considered as a region that provides a more desirable trade off point between delay and power dissipation compared with that of the sub threshold one, because it results in lower delay compared with the sub threshold region and significantly lowers switching and leakage powers compared with the super threshold region. In addition, near-threshold operation, which uses supply voltage levels near the threshold voltage of transistors [11], suffers considerably less from the process and environmental variations compared with the sub threshold region. The dependence of the power (and performance) on the supply voltage has been the motivation for design of circuits with the feature of dynamic voltage and frequency scaling. In these circuits, to reduce the energy consumption, the system may change the voltage (and frequency)of the circuit based on the work load requirement[12]. For these systems, the circuit should be able to operate under a wide range of supply voltage levels. Of course, achieving higher speeds at lower supply voltages for the computational blocks, with the adder as one the main components, could be crucial in the design of high-speed, yet energy efficient, processors. In addition to the knob of the supply voltage, one

may choose between different adder structures/families for optimizing power and speed. There are many adder families with different delays ,power consumption

#### II. RELATED WORK

In this paper, given the attractive features of the CSKA structure, we have focused on reducing its delay by modifying its implementation based on the static CMOS logic. The concentration on the static CMOS originates from the desire to have are liably operating circuit under a wide range of supply voltages in highly scaled technologies [10]. The proposed modification increases the speed considerably while maintaining the low area and power consumption features of the CSKA. In addition, an adjustment of the structure, based on the variable latency technique, which in turn lowers the power consumption without considerably impacting the CSKA speed, is also presented. To the best of our knowledge, no work concentrating on design of CSKAs operating from the super threshold region down to near-threshold region and also, the design of(hybrid) variable latency CSKA structures have been reported in the literature. Hence, the contributions of this paper can be summarized as follows.

- 1) Proposing a modified CSKA structure by combining the concatenation and the incrementation schemes to the conventional CSKA (Conv-CSKA) structure for enhancing the speed and energy efficiency of the adder. The modification provides us with the ability to use simpler carry skip logics based on the AOI/OAI compound gates instead of the multiplexer.

- 2) Providing a design strategy for constructing an efficient CSKA structure based on analytically expressions presented for the critical path delay.

- 3) Investigating the impact of voltage scaling on the efficiency of the proposed CSKA

ISSN: 2456 - 5083

A Peer Revieved Open Access International Journal

www.ijiemr.org

structure(from the nominal supply voltage to the near-threshold voltage).

4) Proposing a hybrid variable latency CSKA structure based on the extension of the suggested CSKA, by replacing some of the middle stages in its structure with a PPA, which is modified in this paper.

There is to this paper is organized as follows. Section II discusses related work on modifying the CSKA structure for improving the speed as well as prior work that use variable latency structures for increasing the efficiency of adders at low supply voltages. In Section III, the Conv-CSKA with fixed stage size (FSS) and variable stage size(VSS)is explained, while Section IV describes the proposed static CSKA structure. The hybrid variable latency CSKA structure is suggested

#### III. CARRY SKIP ADDER

Modifying CSKAs for Improving Speed.The conventional structure of the CSKA consists of stages containing chain of full adders (FAs) (RCA block) and2:1multiplexer (carry skip logic). The RCA blocks are connected to each other through 2:1multiplexers, which can be placed in to one or more level structures [19]. The CSKA configuration (i.e., the number of the FAs per stage) has a great impact on the speed of this type of adder [23]. Many methods have been suggested for finding the optimum number of the FAs [18]-[26]. The techniques presented in[19]-[24]make use of VSSs to minimize the delay of adders based on a singlelevel carry skip logic. In[25],some methods to increase the speed of the multilevel CSKAs are proposed. The techniques, however, cause area and power increase considerably and less regular layout. The design of a static CMOS CSKA where the stages of the CSKA have a variable sizes was suggested in[18]. In addition, to lower the propagation delay of the adder ,in each stage, the carry look-ahead logics were utilized. Again, in that complex layout as well as large power consumption and area usage. In addition, the design approach, which was presented only for the 32-bit adder, was not general to be applied for structures with different bits lengths.

### IV. EXPERIMENTAL RESULTS

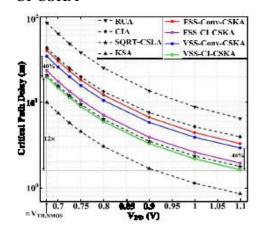

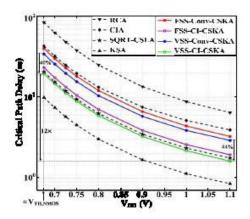

In this areas with those of some other adders. All the adders considered here had the size of 32 bits and were designed and simulated using a 45-nm static CMOS technology [38]. The simulations were performed using HSPICE [40]in the room temperature of 25 °C. The nominal supply voltage of the technology was 1.1 V, and the threshold voltages of Then MOS and pMOS transistors were 0.677 and -0.622V, respectively. It should be noted that, to extract the power consumption of the adders, 10000 uniform random stimuli were injected to them .In addition .for each adder structure in each supply voltage level ,the injection rate of the stimuli was chosen based on the maximum operating frequency of the structure. In the following Section VI- A and Section VI-B, we first concentrate on studying the effectiveness of the pro- posed CI-CSKA structure and then investigate the efficiency of the proposed hybrid variable latency structure based on the CI-CSKA

ISSN: 2456 - 5083

A Peer Revieved Open Access International Journal

www.ijiemr.org

FIG.8. CRITICAL PATH DELAY OF THE ADDERS VERSUS THE SUPPLY VOLTAGE.

### **V.CONCLUSION**

In the proposed hybrid structure ,the prefix network of the Brent-Kung adder[39] is used for constructing the nucleus stage(Fig.7).One the advantages of the this adder compared with other prefix adders is that in this structure, using forward paths, the longest carry is calculated sooner compared with intermediate carries ,which are computed by back ward paths. In addition, the fan-out of adder is less than other parallel adders, while the length of its wiring is smaller[14]. Finally, it has a simple and regular layout. The internal structure of the stage p, including the modified PPA and skip logic

#### REFERENCES

- [1] i.koren, computer arithmetic algorithms ,2nded .natick ,ma,usa: akpeters,ltd.,2002.

- [2] r. zlatanovici, s. kao, and b. nikolic, "energy–delay optimization of 64-bit carry-look ahead adders with a240ps 90nm cmos design example, "ieee j. solid-state circuits,vol.44,no.2,pp.569–583, feb.2009.

- [3] s. k. mathew, m. a. anders, b. bloechel, t.nguyen, r. k. krishnamurthy, and s. borkar, "a 4-ghz [300-mw 64-bit integer execution alu

ISSN: 2456 - 5083

with dual supply voltages in 90-nm cmos," ieeej.solid-state circuits,vol.40,no.1,pp.44–51,jan.2005.

- [4] v. g. oklobdzija, b. r. zeydel, h. q. dao, s. mathew, and r.krishnamurthy, "comparison of high-performance vlsi adders in the energydelay space, "ieee trans. very large scale integer.(vlsi) syst.,vol.13,no.6,pp.754–758,jun.2005.

- [5] b.ramkumarand h.m.kittur, "low-power and area-efficient carry select adder," ieee trans .very large scale integr.(vlsi) syst.,vol.20, no.2,pp.371–375,feb.2012.

- [6] m.vratonjic, b.r.zeydel, and v.g.oklobdzija, "low-and ultra low-power arithmetic units :design and comparison,"in proc. ieee int .conf.comput.design, vlsi comput.process. (iccd),oct.2005, pp.249–252.

- [7] c.nagendra, m.j.irwin, and r.m. owens, "area-time-power trade offs inparallel adders, "ieee trans.circuits syst.ii, analog digit.signal process.,vol.43,no.10,pp.689–702,oct.1996.

- [8] y.he and c.-h. chang," apower-delay efficient hybrid carry- look ahead/carry-select based redundant binary to two's complement converter, "ieeetrans.circuitssyst.i,reg.papers,vo 1.55,no.1, pp.336–346,feb.2008.

- [9] c.-h.chang,j.gu, and m.zhang,"are view of 0.18µm full adder performances for tree structured arithmetic circuits,"ieee trans .very large scale integr.(vlsi)syst.,vol.13,no.6,pp.686–695,jun.2005.

- [10] d.markovic, c.c.wang, l.p.alarcon,t.-t. liu, and j.m.rabaey, "ultra low-power design in near-threshold region," proc .ieee, vol.98, no.2,pp.237–252,feb.2010.

A Peer Revieved Open Access International Journal

www.ijiemr.org

## **AUTHORS**

Mrs, NARABOINA HARIKA

Branch: ECE(Embedded Systems)

Mail id:naraboinaharika@gmail.com

College name: ANURAG ENGINEERING

**COLLEGE**

### KUMMARIKUNTLA SHRAVANI

Branch: VLSI-SD

Mail id: sravs.gates555@gmail.com

College name: ANURAG ENGINEERING

ISSN: 2456 - 5083

**COLLEGE**