PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

## COPY RIGHT

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

2023 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

IJIEMR Transactions, online available on 22 Aug 2022. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-12&issue=Issue 08

## 10.48047/IJIEMR/V12/ISSUE 08/08

Title D-Latch-Based Modified Low-Power and Area-Efficient Carry Select Adder

Volume 12, ISSUE 08, Pages: 46-51

Paper Authors Ranjith S, Naveen Kathula, Vikas Kumar Marka, Arun Teja Mukkera,

Laxmi Prasanna Racharla, Navya Chinthakuntla

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

## D-Latch-Based Modified Low-Power and Area-Efficient Carry Select Adder

Ranjith S<sup>1</sup>, Naveen Kathula<sup>2</sup>, Vikas Kumar Marka<sup>3</sup>, Arun Teja Mukkera<sup>4</sup>, Laxmi Prasanna Racharla<sup>5</sup>, Navya Chinthakuntla<sup>6</sup> Assistant Professor, Dept. of Electronics & Communication Engineering. Balaji Institute

of Technology and Science, Warangal, Telangana, India <sup>2,3,4,5,6</sup> UG Student, Dept. of Electronics & Communication Engineering. Balaji Institute of Technology and Science, Warangal, Telangana, India

**Abstract**—The Carry Select Adder (CSLA) is one of the quick adders used in many computer systems for quickly performing mathematical calculations. The employment of mathematical units that are not just quicker but smaller and lower power is required by the quickly growing mobile sector. When creating the enhanced CSLA architecture, the Converter from Binary to Excess-1 (BEC) was utilised. In place of the BEC, this study proposes a useful method that makes use of a D latch. In terms of power, latency and area, experimental study shows that the suggested architecture offers triple benefits.

Keywords— Low Power, Area Efficient, CSLA, and BEC

## I. Introduction

Building high-speed data route logic systems<sup>[1]</sup> that are both power and area efficient is one of the most crucial study areas in VLSI system design. The time it takes a carry to go through an adder limits the pace of addition in digital adders. In an elementary adder, each bit location's Only when the sum and a carry have been transferred into the following bit position from the previous bit position is sum created sequentially. In multiple computational systems, the CSLA is used to independently generate several carries before choosing one of them to produce the sum. A compromise between the ripple carry adder's (RCA) smaller area and longer delay and the carry look-ahead adder's larger area and shorter delay is provided by the<sub>[2]</sub> carry-select adder (CSLA). The carry inputs Cin=0 and Cin=1 are taken into consideration when using several pairs of ripple carry adders (RCA) to construct partial sum and carry in the CSLA algorithm. The final total is then selected and carried by multiplexers. The redesigned CSLA using BEC has a minor increase in delay with a reduction in area and power consumption. The suggested architecture's fundamental concept is to replace the BEC with a D latch and an enable signal. The area, latency, and power are reduced by the suggested architecture. Following is the organizational structure of this work; section III details the structure and operation of the binary to excess-1 converter logic. Sections IV and V,<sup>[3]</sup> respectively, provide explanations of the standard and modified CSLAs. Section VI discusses the intended architecture. The report's seventh section analyses the findings. Section

## II. Literature Survey

Low-power and space-efficient carry-select adder, IEEE Trans. Very Large Scale Integrated (VLSI) Syst., vol. 20, no. 2, February 2012, pp. 371-375. Ramkumar, B., and Kittur, H. M. They proposed a layout where a BEC-1 block known as the binary to recess one converter would substitute for the ripple carry block in a conventional CSLA layout. The basic idea behind this effort is to use BEC rather than RCA because BEC-1 takes up less room and uses less power than a traditional CSLA. Utilizing a binary to excess one converter is the intended alternative to using RCA with carry equal to one. There is a flaw in this project that will make it take longer than current procedures.

[2] Yajun. He, C. H. Chang, and J. Gu's article, "An area-efficient 64-bit square root carry select adder for low power application," was published in Proc. IEEE Int. Symp. Circuits Syst. in 2005. They gave information on a brand-new, spaceeffective square root CSL technique based on the first zero detection logic. The adder is divided into several groups using a carry-select adder, and each group does two additions simultaneously. As a result, the carry assessment blocks in each chosen step are two ripple-carry adders. When analyzing the carry chain, the block carry-in is assumed to be zero in one copy and one in the other copy.

[3] Chyn Wey, Cheng-Chen Ho, Yi-Sheng Lin, and Chien-Chang Peng published An Area- In the Proceedings of the International Multi Conference of Engineers, Efficient Carry Select Adder Design by Sharing the Common Boolean Logic Term and

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

Computer Scientists 2012 Vol II, IMECS 2012, March 14–16, 2012, Hong Kong. They proposed an area-efficient carry select adder by using a common boolean logic term. In the conventional carry select adder after boolean simplification, they can get rid of the redundant adder cells. The carry-out and sum signals are instead repeated in each cell of the single-bit adder.

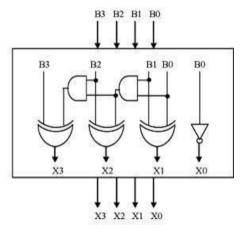

## III. BEC

To decrease the size and power consumption of traditional CSLA, BEC is utilized in place of the RCA with Cin=1. The n-bit RCA is replaced with an n+1 bit BEC. Figure 1 and Table 1 each display the function table for a 4-b BEC. BEC logic allows us to greatly reduce the silicon area reduction in the VLSI design. The 3-bit BEC's corresponding Boolean equations are listed below.

S0=B0, B1=B0, B1, and S2=B2 are equal to B0 and B1, respectively.

Fig. 1 4-Bit BEC

|  | TABLE. | FUNCTION | TABLE OF | 4-BIT BEC |

|--|--------|----------|----------|-----------|

|--|--------|----------|----------|-----------|

| B[3:0] | X{3:0} |

|--------|--------|

| 1111   | 0000   |

| 1110   | 1111   |

| -      | -      |

| -      | -      |

| -      | -      |

| 0001   | 0010   |

| 0000   | 0001   |

## **IV. SQRT REGULAR CSLA**

www.ijiemr.org

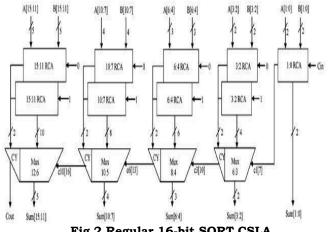

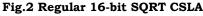

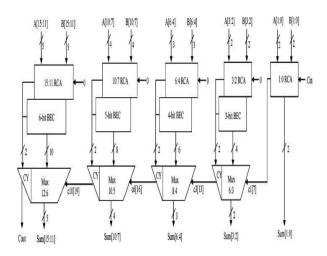

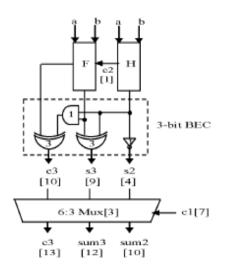

Figure 5 depicts the 16-b standard SQRT CSLA's structure. It includes five RCA groups of various sizes. Fig. 2 displays the delay and area evaluation for each group, with the delay values denoted by the numbers within []. The actual determined values of the output carry and total are chosen using the carry out calculated from the final step, or least significant bit stage. A multiplexer is employed in the selection process. Fig. 3 depicts the internal organization of group 2 of the standard 16-bit CSLA. By hand counting, there are 57 gates (full adder, half adder, and multiplexer) utilized in group 2. The mux receives two RCA inputs, one with Cin=0 and the other with Cin=1. Two sets of 2-b RCA are present in group 2. Selection input c1 arrives at 6:3 mux at the time (t) = 7, which is before s3 (t = 8) and after s2 (t = 6) respectively. As a result, Summation of c1 and mux is sum2 [t = 10], while sum3 [t = 11] is the summation of s3 and mux [t = 3].

Fig.3 Group 2

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### **V.MODIFIED CSLA USING BEC**

Fig. 4 depicts the topology of the 16-b SQRT CSLA that has been suggested, employing BEC for RCA with Cin=1 to maximize space and power. We divided the structure into five groups once more. Fig. 5 displays the delay and area estimation for each group 2 participant. The RCA with Cin=0 provides one input to the mux, and the BEC provides the other. It is evident from a comparison of group 2 of both standard and modified CSLA that the BEC structure reduces area and power. However, the BEC technique has the drawback of having a longer delay than the standard CSLA.

Fig 4:CSLA using BEC

Fig. 5 Group II

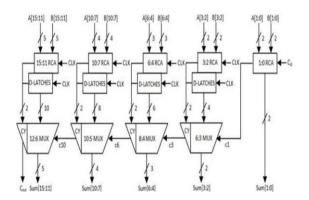

#### VI.MODIFIED 16-BIT CSLA USING D-LATCH

www.ijiemr.org

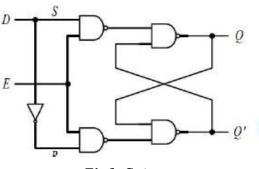

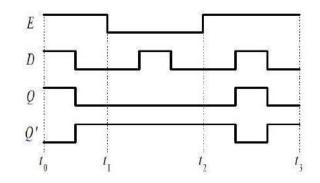

With this technique, a D-latch and an enable signal replace the BEC and add one circuit. One piece of data is stored via latches. Their outputs are continuously influenced by their inputs as long as the enable signal is asserted. In other words, when they're activated, their content instantly adapts to user input. The D-latch and its waveforms are seen in Figures 6 and 7.

Fig6: Gates

Fig 7: Input and output Waveforms

## Fig8: Modified CLSA Using D-LATCH

It displays the group 2 internal structure of the suggested 16-bit CSLA. The two-bit addition was carried out by group 2 using the pairs a2 and b2, a3, and b3. This is done by the two full adders (FA), FA2 and FA3, in turn.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

The carry output from FA2 serves as the third input to the full adder FA2, and the clock serves as the third input to the full adder FA3. Five D-Latches make up the group 2 structure, four of which is used to store carry, while the fifth is used to store the sum2 and sum3 from FA2 and FA3, respectively. The real total and carry are chosen using a multiplexer based on the carry from the previous stage. The 2:1 multiplexer and the 6:3 multiplexer are combined a2 and b2 are added with a carry of 0, when the clock is low. Due to the low clock, the initial D-Latch is not enabled. Using an inverted clock enable, the second D-Latch stores the sum when cosine equals 0. The addition is performed with a carry of 1 when the clock is ticking quickly. The total of the other enabled D-Latches that the store carry for carry is one. Whether c1 had a value of 0 or 1 determined the real sum and carry the multiplexer would use.

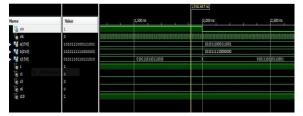

## **VII.SIMULATION RESULTS**

A. Waveforms

# Name Value 1,500 ns 2,500 ns 2,500 ns 3,000 ns ▶ ♥ \$15.00 111000111000 1110001110001110 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Fig.9 Regular SQRT CSLA Simulation

Fig.10 D-Latch-enhanced modified CSLA

**B.** Power Report

| I Por                     | er Supply Summary                        | 1                             |

|---------------------------|------------------------------------------|-------------------------------|

| l.                        | Total   Dynamic   Q                      | Quiescent                     |

| Supply Power (mW)         | 1710.63   1654.98   5                    | 15.65                         |

| l<br>I                    | P                                        | Power Supply Currents         |

|                           |                                          |                               |

|                           | Supply Voltage   Tot<br>ent Current (mA) | al Current (mA)   Dynamio     |

| Current (mA)   Quieso<br> | ent Current (mA)  <br>                   | al Current (mA)   Dynamid<br> |

| Current (mA)   Quieso     | ent Current (mA)                         |                               |

www.ijiemr.org

#### Fig .11 Power report of Regular SQRT CSLA

2.3. Power Supply Summary

| I |        |       | Power | SI | upply S | um | mary    |          |           | 1 |

|---|--------|-------|-------|----|---------|----|---------|----------|-----------|---|

| ī |        |       |       | J  | Total   | ļ  | Dynamic | <u>I</u> | Quiescent | ļ |

| 1 | Supply | Power | (mW)  | I  | 874.37  | 1  | 827.49  | 1        | 46.88     | 1 |

|                  |           |                   |                 | Power Supply Currents |                 |         |  |  |

|------------------|-----------|-------------------|-----------------|-----------------------|-----------------|---------|--|--|

|                  | Quiescent | Supply<br>Current | Voltage<br>(mA) | Tot                   | al Current (mA) | Dynamic |  |  |

| Vccint<br>7.59   |           | 5.11              | 1.200           | 1                     | 22.70           | ) [     |  |  |

| Vccaux           |           | 10.00             | 2.500           | 1                     | 26.95           | 5 I     |  |  |

| Vcco25<br>310.40 | )         | 1.50              | 2.500           | 1                     | 311.90          | 1       |  |  |

#### Figure.12, Regular SQRT CSLA Power Report

#### 2.3. Power Supply Summary

| l |        |       | Power | S | upply S | Sum | mary    |   |           | I  |

|---|--------|-------|-------|---|---------|-----|---------|---|-----------|----|

| I |        |       |       | 1 | Total   | 1   | Dynamic | I | Quiescent | ī  |

| ī | Supply | Power | (mW)  | Ţ | 324.21  | 1   | 281.48  | Ļ | 42.73     | ī, |

| I.                               |                     |       | Power Supply Currents |                |         |  |

|----------------------------------|---------------------|-------|-----------------------|----------------|---------|--|

| Supply Sou:<br>Current (mA)   Qu |                     |       | Tota                  | l Current (mA) | Dynamic |  |

|                                  | 1                   | 1.200 | 1                     | 246.22         | I.      |  |

| Vccint<br>234.57                 | 11.65               | 1     |                       |                |         |  |

|                                  | 11.65<br> <br>10.00 | 2.500 | 1                     | 10.00          | l,      |  |

#### Fig. 13. Modified CSLA power report utilizing D-Latch

Vol 12 Issue 08, Aug 2023

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

## TABLE III COMPARISON

| (16-bit) Adder                    | Delay(n<br>s) | Power(mW) | PDP(x10<br>^_<br>12) |

|-----------------------------------|---------------|-----------|----------------------|

| SQRT Regular<br>CSLA              | 21.07         | 1715.42   | 34411.2              |

| CSLA using<br>BEC                 | 21.678        | 882.37    | 18684.64             |

| Modified CSLA<br>using<br>D-Latch | 17.09         | 324.21    | 5783.90              |

## VII.CONCLUSION

This study suggests a straightforward method for reducing the size and power of SQRT CSLA architecture. This work's fewer gates have a significant benefit in terms of reduced area and overall power (Table II). By using a Binary to Excess-1 converter, In comparison to a standard CSLA, the modified CSLA reduces area and power while increasing latency. By utilizing Dlatches, the technique proposed in this research reduces delay, area, and power compared to normal and modified CSLA.

## REFERENCES

- O. J. Bedrij, -Carry-select adder, IRE Trans. Electron. Comput., pp. 340–344, 1962.

- [2] B. Ramkumar, H.M. Kittur, and P. M. Kannan, -ASIC implementation of modified faster carry save adder, Eur. J. Sci. Res., vol. 42, no. 1, pp. 53–58, 2010.

- [3] T. Y. Ceiang and M. J. Hsiao, -Carry-select adder using single ripple carry adder,∥ Electron. Lett., vol. 34, no. 22, pp. 2101– 2103, Oct. 1998.

- [4] Y. Kim and L.-S. Kim, -64-bit carry-select adder with the reduced area, I Electron. Lett., vol. 37, no. 10, pp. 614–615, May 2001.

- Padakanti Kiran Kumar, Bukya [5] Balaji, K.Srinivasa Rao, Design and analysis of asymmetrical low-k source side spacer doped halo nanowire metal oxide semiconductor field effect transistor, IJECE, Vol 13. No 3 DOI: http://doi.org/10.11591/ijece.v13i3.p p3519-3529.

- [6] P. K. Kumar, K. Srikanth, N. K. Boddukuri, N. Suresh and B. V. Vani,

"Lattice Heating Effects on Electric Field and Potential for a Silicon on Insulator (SOI) MOSFET for MIMO Applications," 2023 2nd Edition of IEEE Delhi Section Flagship Conference (DELCON.

www.ijiemr.org

- P. K. Kumar, P. P. Rao and K. H.

Kishore, "Optimal design of reversible parity preserving new Full adder / Full subtractor,"

2017 11th International Conference on Intelligent Systems and Control (ISCO.

- [8] V.Madhu Kumar, Dr.T.V.Ramana" Virtual Iterative Precoding Based LTE POMA Channel Estimation Technique in Dynamic Fading Environments" International Journal of Innovative Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-8 Issue-6, April 2019

- Kumar, Dr.T.V. Ramana, [9] V.Madhu Rajidi Sahithi" User Content Delivery Service for LTE Efficient POMA based Channel Spectrum Scheduling Algorithm" International Innovative Journal of Technology and Exploring Engineering (IJITEE) ISSN: 2278-3075, Volume-9 Issue-2S3, December 2019

- [10] Madhu Kumar Vanteru, K.A. Jayabalaji, Suja G. P, Poonguzhali Ilango, Bhaskar Nautiyal, A. Yasmine Begum,Multi-Sensor Based healthcare monitoring system by LoWPAN-based architecture,Measurement: Sensors,Volume 28,2023,100826,ISSN 2665-9174.

- [11] Dr.M.Supriya, Dr.R.Mohandas. (2022). Multi Constraint Multicasting Analysis with fault Tolerance Routing Mechanism. Telematique, 21(1), 3544-3554.

- [12] N.Sivapriya, T.N.Ravi. (2019). Efficient Fuzzy based Multi-constraint Multicast Routing with Multi-criteria Enhanced Optimal Capacity-delay Trade off. International journal of Scientific & Technology Research, 8(8), 1468-1473.

- [13] N.Sivapriya, T.N.Ravi. (2019). A framework for fuzzy-based Fault Tolerant Routing Mechanism with Capacity Delay Tradeoff in MANET. International Journal of advanced Science & Technology, 28(17), 420-429.

- [14] Kumar, V. & Ramana, T.. (2022). Fully scheduled decomposition channel estimation based MIMO-POMA structured LTE. International Journal of Communication Systems. 35. 10.1002/dac.4263.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

- [15] V. M. Kumar and T. V. Ramana, "Positionbased Fully-Scheduled Precoder Channel Strategy for POMA Structured LTE Network," 2019 IEEE International Conference on Electrical, Computer and Communication Technologies (ICECCT), Coimbatore, India, 2019, pp. 1-8, doi: 10.1109/ICECCT.2019.8869133.

- [16] Karthik Kumar Vaigandla and B. J, Study and analysis of multi carrier modulation techniques - FBMC and OFDM, Materials Today: Proceedings, Volume 58, Part 1, 2022, Pages 52-56, Karthik Kumar Vaigandla, J.Benita, "PRNGN - PAPR Reduction using Noise Validation and Genetic System on 5G Wireless Network," International Journal of Engineering Trends and Technology, vol. 70, no. 8, pp. 224-232, 2022.

- [17] Karthik Kumar Vaigandla and J.Benita (2022), Novel Algorithm for Nonlinear Distortion Reduction Based on Clipping and Compressive Sensing in OFDM/OQAM System. IJEER 10(3), 620-626. <u>https://doi.org/10.37391/IJEER.100334</u>