PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

### COPY RIGHT

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors JJIEMR Transactions, online available on 05<sup>th</sup> Apr 2023. Link

2023 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

:http://www.ijiemr.org/downloads.php?vol=Volume-12&issue=Issue 04

### 10.48047/IJIEMR/V12/ISSUE 04/26

Title QUANTUM GATES BASED CARRY SELECT ADDER USING VHDL

Volume 12, ISSUE 04, Pages: 198-205

Paper Authors

G. Kumar Sai Sandeep, J.D.V.Sai Krishna, A.Lohit Sai, A.Sai Kiran

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

### Quantum Gates Based Carry Select Adder Using VHDL

**G. Kumar Sai Sandeep<sup>1</sup>**, **J.D.V.Sai Krishna<sup>2</sup>**, **A.Lohit Sai<sup>3</sup>**, **A.Sai Kiran<sup>4</sup>** <sup>1,2,3,4</sup> UG Students, Department of ECE, Vasireddy Venkatadri Institute of Technology, Nambur, Guntur Dt., Andhra Pradesh. <sup>1</sup>gkssandeep6@gmail.com, <sup>2</sup>venkatasaijetti@gmail.com, <sup>3</sup> lohitsaiannam9@gmail.com , <sup>4</sup>saikiranreddyannapureddy@gmail.com

#### Abstract

Quantum computing is indeed a promising technology that utilizes the principles of quantum mechanics to perform computations that are beyond the capabilities of classical computers. In this context, the design of adders using low quantum cost full adder is a significant step towards building practical quantum circuits.

The proposed full adder design based on CNOT and CCNOT gates is a common approach used in many quantum circuits. The parallel adder and carry select adder designed using this full adder are also valuable contributions that demonstrate the potential of quantum computing. The use of CSWAP gates in the proposed carry select adder design is an interesting choice, as CSWAP gates are known to have a low quantum cost compared to other multi-qubit gates. The use of CSWAP gates as 2×1 multiplexers is a clever way to select the output from the two parallel adders that make up the carry select adder.

It is worth noting that the simulation of quantum circuits using tools such as Xilinx Vivado is an essential step in the design process. Simulations provide a means to verify the correctness of the circuit and observe its behavior under different conditions. Overall, the design of adders using low quantum cost full adder is a significant contribution to the field of quantum computing. It paves the way for the development of more complex quantum circuits that can solve real-world problems efficiently.

**Keywords:** Carry Select Adder, CSWAP Gate, CCNOT Gate, Quantum Circuits, Xilinx Vivado

#### Introduction

The demand for high-speed information processing and computation in various fields has led to the development of complementary metal oxide semiconductor (CMOS) technology. However, despite its usefulness, CMOS still faces limitations due to high-speed requirements. This has led to the development of quantum computing as an alternative to classical computing systems.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

Quantum computing is advantageous due its properties of interference, to entanglement, superposition, and reversibility. These properties make it suitable for various applications, including communication and complex computational problems. Ouantum researchers have been working on developing quantum logic gates, which are the building blocks of quantum circuits. These gates manipulate the state of qubits, which are the basic units of quantum information.

Arithmetic and logical operations are crucial for many practical applications of quantum computing, such as cryptography and optimization. Therefore, researchers have been exploring ways to implement these operations using quantum gates.

Qubit characterization is also an important area of research in quantum computing. Since qubits are susceptible to various sources of noise and errors, it is essential characterize their to properties accurately. This involves measuring various parameters such as coherence time, fidelity, and error rates, which can help researchers optimize the performance of quantum circuits.

Overall, the design of logic systems and improving decision-making abilities using quantum gates and qubit characterization are crucial steps towards building practical quantum computers that can outperform classical computers in specific tasks. In this article, the authors propose a full adder with low quantum cost and garbage output, which is then used to design a 4-bit parallel adder and carry select adder. The authors use a CSWAP gate as a multiplexer for the design of the carry select adder. The proposed quantum circuits are designed and simulated using the open-source Xilinx Vivado software with VHDL programming.

In section I, the discussion on available quantum operators to design logic gates and single bit adders is essential as it provides readers with the necessary background information on quantum gates and their properties. This section can help readers understand the basics of quantum computing and prepare them for the subsequent sections.

Section III, which explains the design of the parallel adder and carry select adder using the full adder, is a crucial part of the article. This section provides readers with a detailed description of the proposed quantum circuits and how they can be built using the full adder. This section can help readers understand how to design more complex quantum circuits using simpler building blocks.

Section IV, which analyzes the outcome of the simulated quantum circuits with respect to metrics, is also an important part of the article. This section provides readers with a quantitative assessment of the proposed quantum circuits' performance, which can help them evaluate the usefulness of the proposed approach.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

Finally, section V, which concludes the proposed work, is an essential part of the article as it summarizes the key findings and contributions of the proposed work. This section can help readers understand the overall impact of the proposed work on the field of quantum computing. Overall, the proposed low quantum cost full adder and the resulting parallel adder and carry select adder designs show promise in improving the speed and efficiency of quantum computing systems. Further research and development in this field are needed to improve the design and implementation of quantum circuits for practical applications.

#### Quantum Gates Based 1-Bit Adders

Two-level qubit systems are the simplest form of quantum systems that are widely used in quantum computing. These systems operate over two states, commonly denoted as  $|0\rangle$  and  $|1\rangle$ , which form the basis for quantum computation. These states are also referred to as the computational basis states.

$$|0\rangle = \begin{pmatrix} 1\\ 0 \end{pmatrix}, \qquad |1\rangle = \begin{pmatrix} 0\\ 1 \end{pmatrix}$$

(1)

These qubit states are analogous to the binary elements or bits of the classical systems, '0' and '1'. But these states  $|0\rangle$  and  $|1\rangle$  differ from classical system in another form of state, which is a linear combination or superposition of both.

The article states that only a few operators are described in the later part of the section, which are required for the proposed designs. It is not clear which specific operators are being referred to, as the article does not provide further details.

In quantum mechanics, the state of a qubit can be represented using a complex vector in a two-dimensional Hilbert space. The state vector of a qubit can be expressed as a linear combination of the basis states  $|0\rangle$  and  $|1\rangle$ :

$$|\psi\rangle = \alpha \,|\,0\rangle + \beta \,|\,1\rangle,$$

where a and  $\beta$  are complex numbers, and  $|\alpha|^2 + |\beta|^2 = 1$ , which reflects the normalization condition for a quantum state. This superposition property of qubits is one of the fundamental differences between classical and quantum computing.

The ability to manipulate the state of qubits using quantum gates and perform operations on superposed states is what makes quantum computing powerful and capable of solving problems that are intractable for classical computers.

Therefore, understanding two-level qubit systems and their properties is essential for analyzing quantum circuits, defining quantum algorithms, and developing quantum computers.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

#### A. Unary Gates: I,X and H

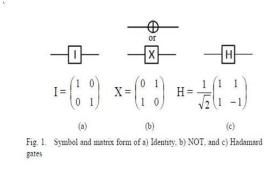

According to the article, there are three unary gates commonly used in quantum computing: Identity (I), NOT (X), and Hadamard (H). These gates operate on a single qubit, and their matrix representations are shown in Figure 1 along with their symbols.

The Identity gate, represented by the symbol I, does not change the input qubit and provides the same qubit as an output. The NOT gate, represented by the symbol X, flips the input qubit, changing  $|0\rangle$  to  $|1\rangle$  and vice versa.

The Hadamard gate, represented by the symbol H, is an important gate in quantum computing and information systems. It transforms a qubit into a superposition of its computational basis states [4]. If an input qubit system is applied with n Hadamard gates, outputs will be produced for all possible input combinations.

#### **B.** Binary and Ternary Gates:

It is common to represent quantum gates using symbols that depict their functionality. These symbols can help readers understand the operation of quantum gates without going into the details of their underlying quantum mechanics.

www.ijiemr.org

In the context of the article, Fig. 2 likely shows the symbols of quantum gates that are relevant to the proposed work. The first gate is likely a binary gate, which operates on two qubits and performs a binary operation, such as the CNOT(Feynman )gate. The remaining two gates are likely ternary gates, which operate on three qubits and perform a ternary operation, such as the CCNOT (Toffoli) gate.

The symbols of these gates can vary depending on the notation used by different authors or in different contexts. However, the logical operations performed by these gates are typically standardized and represented using truth tables or other forms of logical expressions. These logical operations can help readers quantum understand how gates manipulate the state of qubits and perform various arithmetic and logical operations that are relevant to quantum computing.

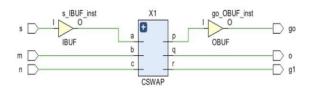

The CSWAP gate is also named the Fredkin gate and is a controlled SWAP gate that can be used for swapping, AND, and OR operations.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

The design metrics used in the proposed work are Constant Inputs (CI), Garbage Outputs (GO), and Quantum Cost (QC).

Garbage outputs are gate outputs that are not considered as primary outputs and are not connected to any other gate.

Constant inputs are gate inputs that are excited with logic '0' or logic '1' to obtain the required output.

#### Literature Survey

The paper [1] proposed by Dr.Sk.Enaul Haq consists of the details about Quantum gates and Carry select adder developed using IBM Qiskit.

The paper [2] proposed by T.S Humble contains the details about quantum computing circuits and devices which helps us to develop carry select adder.

The paper [3] proposed by H.Thomas tells us about the programming of the quantum circuits which helps us to write the programms for the quantum circuits.

#### **Problem Identification**

The Early Model of the Carry Select Adder is developed in python by using IBM Qiskit which is taking more time than expected and requires large circuits hence we want to design the circuit in the low cost which works faster than the earlier version and which takes the less gates to build the circuit.

#### Methodology

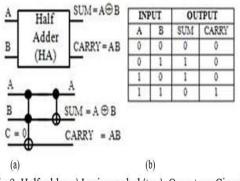

The following are the Design methodology steps to develop Carry select adder: Step 1: Build the Halfadder circuit using the Quantum gates like cnot and ccnot.

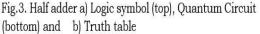

Step 2: After creating the Half Adder using Quantum gates then try to create the full adder circuit just by cascading the two half adders.

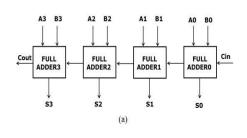

Step 3: After creating the full adder then we have to cascade the four full adders to generate the parallel adder.It will generate 4 bit parallel adder.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

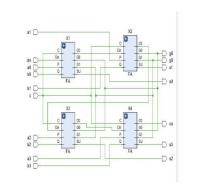

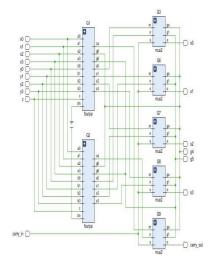

Fig. 5. Parallel Adder (a) Block diagram and (b) Quantum Circuit

Step 4: After creating the 4 bit parallel adder then the next step is to create the multiplexer which is used for selection lines.

#### Fig.6.Multiplexer Schematic Diagram

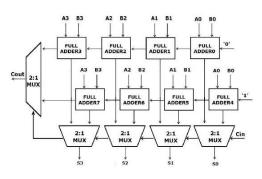

Step 5: After creating multiplexer then cascade two 4 bit parallel adder and 5 multiplexers to get the carry select adder which will be our final circuit design. To select the required output of the carry select adder multiplexers are used in the circuit.

Hence the required carry select adder using full adder and multiplexer is designed and is shown in Figure.

Block diagram of carry select adder

#### Results:

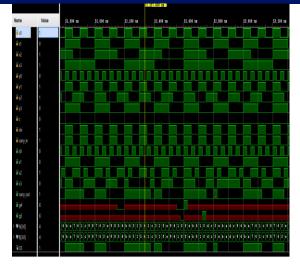

The simulated Results and schematic quantum circuit of the generated carry select adder is given in the below diagrams.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

Carry select adder simulation

#### Conclusion

It's interesting to see how quantum computing is being explored as a potential solution to the limitations of classical computing. The use of quantum gates to design adder circuits is a promising area of research as it has the potential to significantly speed up arithmetic operations.

The low quantum cost of the proposed full adder circuits is also noteworthy as it indicates that they require fewer quantum resources to execute, making them more efficient.

It would be interesting to see further research in this area to explore the potential of quantum computing in solving other complex computational problems. The use of Xilinx Vivado for simulation is also a common practice in digital circuit design and verification.

Quantum Gates based Carry Select Adder can also be implemented using FPGA Kit.

#### Future scope:

There is a scope to improve the effeciency and the speed of the circuits by decresing the delay in the gates.

#### References

- [1] Maheswari R, Shaistha S, Sravani U, Monika V and Enaul Haq Shaik, "CSWAP Operator as 2×1 Multiplexer to Design CNOT and CCNOT Gates based Carry Select Adder," IEEE International Conference on Communication, Control and Information Sciences (ICCISC-2021), 16th - 18th June 2021, Government Engineering College, Idukki, Kerala.

- T.S. Humble, H. Thapliyal, M-C. Edgard, F.A. Mohiyaddin, and R.S.Bennink, "Quantum computing circuits and devices," IEEE Design and Test, vol. 36, pp. 69-94, April 2019

- W.D. Pan, and M. Nalasani, "Reversible logic," IEEE Potentials, vol. 24, pp. 38-41, March 2005. J.M. Shalf, and R. Leland, "Computing beyond Moore's law," Computer, vol. 48, pp. 14-23, December 2015.

- [4] T.M. Conte, E. Track, and E. DeBenedictis, "Rebooting computing: New strategies for technology scaling," Computer, vol. 48, pp. 10-13, December 2015.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

- [5] A. Anand, B.K. Behera, and P.K. Panigrahi, "Solving diner's dilemma game, circuit implementation and verification on the IBM quantum simulator," Quantum Inf. Process. vol. 19, pp. 1-14, May 2020.

- [6] J.D. Hidary, Quantum Computing:

An Applied Approach, Springer

Nature, Switzerland AG, 2019, pp. 3-10.

- M. Soeken, H. Thomas, and R.

Martin, "Programming quantum computers using design automation," proceedings of Design, Automation and Test in Europe, March 2018.

- [8] M.S. Islam and M. Rafiqul Islam, "Minimization of reversible adder circuits," Asian Journal of Information Technology, vol. 4, pp. 11461151, 2005.

- [9] C. Degen, F. Reinhard, and P. Cappellaro, "Quantum sensing: Reviews of modern physics," vol. 89, pp. 035002, July 2017.

- [10] M. Krenn, M. Malik, T. Scheidl, R.

Ursin, and A. Zeilinger, "Quantum communication with photons,"

Optics in Our Time, Springer, December 2016

- [11]V. Vedral, A. Barenco, and A. Ekert, "Quantum networks for elementary arithmetic operations," *Physical Review A*, vol. 54, no. 1, pp. 147–153, July 1996.

- [12]H. Thapliyal, "Mapping of subtractor and adder-subtractor circuits on reversible quantum gates," Trans. on

Comput. Sci. XXVII, LNCS 9570, pp. 10–34, April 2016.

www.ijiemr.org

- [13] M. Rahmati, M. Houshmand, and M.H. Kaffashian, "Novel designs of a carry/borrow look-ahead adder/subtractor using reversible gates," J. Comput. Electron., vol.16, pp. 856-866, July 2017.

- [14] G. Oktay, K.T. Weng, B-F. Kent, and A. Brodutch, "Benchmarking quantum processors with a single qubit," Quantum Inf. Process. vol. 19, pp. 1-17, March 2020.

- [15] J. Wang, and K. Choi, "A carry Look-ahead adder designed by reversible logic", Proceedings of IEEE International SoC Design Conference, pp.216-217, November 2014.

- [16] E.H. Shaik, and N. Rangaswamy, "Implementation of quantum gates based logic circuits using IBM Qiskit," Proceedings of 5th International Conference on Computing, Communication and Security, October 2020.