PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

### Low Power Redundant-Transition-Free TSPC Dual-Edge-Triggering Flip-Flop using Single-Transistor-Clocked Buffer

#### G. Rajya Lakshmi, Dr. K. Sudhakar, Mr. T. Chakrapani

Studying M. tech (vlsi system design ) in ECE Department, St. Johns College of Engineering and Technology, Yerrakota, YEMMIGANUR, Kurnool (dt) A.P. mail.i.d:- graji3211@gmail.com

Professor and H.O.D. in ECE Department, St. Johns College of Engineering and Technology, Yerrakota, YEMMIGANUR, Kurnool (dt) A.P. mail.i.d:- komerasudhakar403@gmail.com

(PhD), Reasearch Scholar and Associate Professor in ECE Department, St. Johns College of Engineering and

Technology., Yerrakota, YEMMIGANUR, Kurnool (dt) A.P. mail.i.d:- <u>tchakrapani57@gmail.com</u>

Abstract— In the ongoing GPU/AI era, fip-fop (FF) has become known as one about the processor blocks with the most powerful utilization. To address previously mentioned issue, an novel buffer-based dual-edgetriggering (DET) FF based on single-transistor clocking (STC) is proposed. The STC support, which utilizes a solitary timed semiconductor in the information testing way, totally disposes of the interior and clock excess changes found in other DET plans. approved at 10% exchanging movement involving post-format recreations in 22nm FD-SOI CMOS.

**Index Terms**—dynamic power, dual edge triggering, flip-flop

#### **I**.INTRODUCTION

Power utilization has become one about fundamental worries for CMOS advanced architects, especially in view about strain from ongoing GPU/artificial intelligence brain network processors. sum about handling power used towards prepare man-made intelligence copies each 3.4 months [1].

The timing framework in a cutting edge processor can consume as much as half about all out power [2]. Subsequently, power streamlining has been considered as one about critical parts towards taking care of power dissemination issue referenced previously.

The timing framework about a processor comprises around two fundamental parts: clock distribution networks & flip-flops(FFs). Ordinary single-stage clock FFs process approaching information through handling just a single clock edge at a time, requiring additional power for information handling certain has not yet been created. Dual edge-triggering (DET) FFs utilize both clock edges towards handle information. Since about this, they can keep up with a similar throughput even in wake of splitting clock recurrence.

A fundamental part about advanced gadgets & PC design is flip-flop. It is a parallel data putting away & - moving successive rationale circuit. Consecutive rationale

circuits like registers, counters, & memory components abide undeniably made with goes back & forth.

Clock beats abide standard signals certain synchronize activity about computerized circuits, & they abide reason for activity about a flip-flop. flip-flop stores either moves information in view of clock signal. SR (Set-Reset) flipflop & D (Data) flip-flop abide two most popular varieties about flip-flops.

1. SR Flip-Flop:

The S (Set) & R (Reset) inputs & Q (and  $\overline{Q}$ , either complement about Q)yields abide two sources of info & results about SR flip-flop. Q yield is reset towards 0 when R input is actuated & towards 1 when S input is enacted. Q yield is contrarily addressed through  $\overline{Q}$  yield. "race condition" is a likely issue with SR flip-flop in which two data sources abide enacted at same time & result in an undefinable state.

#### 2. D Flip-Flop:

The D flip-flop has two outputs: Q output &  $\overline{Q}$  (complement about Q) output. Its single input is D (data) input. Q output's state is determined through D input. D input is switched towards Q output when clock signal is activated. Q output changes from high towards low depending on whether D input is high (1) either low (0). Q output is inversely represented through  $\overline{Q}$  output.

In digital systems, flip-flops abide frequently used for control, synchronization, & data storage. It is possible towards construct intricate sequential circuits like registers & counters through joining several flip-flops together. Digital systems & devices such as computers, calculators, & communication devices abide built on these circuits.

Concepts such as dual-edge & single-edge triggering pertain towards how flip-flops & other sequential logic circuits respond towards clock signals.

#### 1. Single-Edge Triggering:

A flip-flop certain only modifies its state on a single edge about clock signal is said towards endure single-edge triggered. Positive-edge triggering, sometimes referred towards as rising-edge triggering, is most prevalent kind about single-edge triggering. When using positive-edge triggering, flip-flop only modifies its state when clock

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

signal crosses rising edge from low towards high. During low-to-high transition, flip-flop is unaffected & maintains its previous state until rising edge occurs. majority about digital systems employ aforementioned kind about triggering extensively.

#### 2. Dual-Edge Triggering:

On other hand, dual-edge triggering enables flip-flop towards alter its state on both clock signal edges. aforementioned indicates certain when clock signal changes from low towards high (rising edge) either from high towards low (falling edge), flip-flop is able towards sample input & update its state. aforementioned gives circuit designers more freedom when creating sequential logic circuits. Less frequently than single-edge triggering, dual-edge triggering is usually employed in specialized applications where precise timing either synchronization requirements abide offer.

Selecting between single-edge & dual-edge triggering is contingent upon particular application & design specifications. Single-edge triggering works well for majority about digital systems & is easier towards implement. Nonetheless, there abide some situations where dual-edge triggering can endure useful, like in highspeed circuit design, protocol implementation, either exact timing control.

#### Single transistor clocked buffer:

A single-transistor clocked buffer, also called a singlestage clocked buffer either a single-transistor latch, is a simple digital circuit certain is used towards amplify & propagate binary signals certain abide timed with a clock signal. It is widely used in digital systems towards drive & isolate signals between different circuit components.

The single-transistor clocked buffer consists about a single transistor (often a MOSFET either CMOS transistor) & a clock signal. clock signal, which is a periodic square wave, controls buffer. design states certain when clock signal is active (high either low), transistor conducts & allows input signal towards flow through towards output. When clock signal is not active, transistor turns off, effectively isolating Known also as a single-stage clocked buffer, single-transistor latch, either a single-transistor clocked buffer, a single-transistor clocked buffer is a simple digital circuit certain can enhance & spread clock-synchronized binary signals. In digital systems, it is commonly used towards drive & isolate signals between different circuit components.

A clock signal & a single transistor (often a MOSFET either CMOS transistor) make up single-transistor clocked buffer. recurrent square wave certain is clock signal controls how buffer operates. When clock signal is active (either high either low, depending on design), transistor conducts & allows input signal towards pass through towards output. When clock signal is not active, transistor turns off & is effectively isolated from circuit.

#### Transmission free TSPC:

Transmission-Free A sequential logic circuit design method called True Single-Phase Clock (TSPC) is used towards create effective latches either flip-flops in digital circuits. It is frequently used in low-power, high-speed applications.

Transmission gates either pass transistors abide needed through conventional flip-flops & latches in order towards transmit data during clock phase. These transmission gates do, however, come with extra delays & power consumption. through doing away with requirement for transmission gates, Transmission-Free TSPC solves these problems & produces better performance & lower power consumption.

The flip-flop is split into two stages in Transmission-Free TSPC: pre-charge & evaluation. aforementioned is a quick synopsis about process:

1. Pre charge Stage: internal nodes about flip-flop abide charged towards a specific voltage level during pre charge phase through activating a pre charge signal. through precharging, it is ensured certain internal nodes abide ready for evaluation before it begins.

2. Evaluation Stage: data signal is applied towards flipflop's input during aforementioned phase. In addition towards pre charge signal, evaluation signal is turned on. Because about this, depending on data input, internal nodes abide either pulled up either pulled down.

3. Latching: evaluation signal is deactivated at conclusion about evaluation phase, & internal nodes hold onto their values until subsequent clock cycle. From these latched values, flip-flop's output is obtained.

Comparing Transmission-Free TSPC towards conventional flip-flops, there abide benefits like lower power consumption, faster processing, & simpler circuitry. through controlling state about internal nodes with complementary logic signals instead about transmission gates, it achieves transmission-free operation.

It is important towards keep in mind, though, certain Transmission-Free TSPC might come with certain drawbacks, like a larger working area & a higher chance about being affected through noise either clock errors. Consequently, particular needs & limitations about digital circuit being implemented determine whether either not aforementioned design technique is appropriate.

Power utilization is one about fundamental worries for CMOS computerized architects, especially considering push from present day GPUs & simulated intelligence brain network processors. How much handling power utilized for artificial intelligence preparing pairs each 3.4 months. [1].

A cutting edge central processor's timing framework can consume up towards half about its all out power [2]. Consequently, it has been accepted certain upgrading its power is one about fundamental keys towards settling power scattering issue referenced previously.

Flip-flops (FFs) & clock dispersion networks abide two primary pieces about a processor's timing framework. Since only each clock edge is handled in turn through customary single-stage clock FFs, there is an additional power above in light about fact certain other clock edge is left dynamic.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

lacking in improvement about information handling. through handling information utilizing both clock edges, dual edge-triggering (DET) FFs can slice clock recurrence down middle while keeping up with a similar throughput.

It is recommended towards use a true single-phase clock (TSPC) in a new DET FF topology towards further minimize its power consumption.

Numerous low-power flip flops, latches, & techniques have been put forth.One about problems with power consumption in DET FFs is certain clocked transistors frequently result in superfluous redundant power consumption overhead, which happens when input data stays same but some about circuit's transistors continue towards switch actively because about circuit topology.

In digital circuits, Single Transistor Clock Dual Edge Triggering (STCDET) technique is used towards increase performance & efficiency about clock signals. It doubles effective clock frequency through enabling use about a clock signal's rising & falling edges towards start circuit operations.

The rising edge about clock signal synchronizes operations in conventional digital circuits. certain being said, it restricts how quickly operations can endure completed. through exploiting clock signal's rising & falling edges, STCDET gets around aforementioned restriction.

The utilization about a single transistor towards produce two non-overlapping clock signals—one for rising edge & another for falling edge—is fundamental principle about STCDET. aforementioned is accomplished through controlling discharge about a capacitor through means about a transistor acting as a switch. capacitor charges when transistor is on & discharges towards produce falling edge clock signal when transistor is turned off.

The effective clock frequency is doubled thanks towards STCDET technique, which enables circuit towards operate on clock signal's rising & falling edges. As a result, digital circuits operate faster & more efficiently without requiring major modifications towards underlying circuitry.

Applications for STCDET can endure found in a variety about digital systems, such as memory interfaces, data communication systems, & high-speed processors, where optimizing clock frequency is essential for effective operation.

#### II. Earlier Works

From an energy & concede point about view, snares & flip-flops abide principal parts about an arrangement. We break down various types about static & semi-dynamic single edge-set off returns & forward with certain & express heartbeat age. We present an implied beat, semi-dynamic flip-flop (ip-DCO) with a ton about regrettable game plan time & speediest delay about any flip-flop

considered. For most fundamental courses in arrangement, in any case, an explicit-pulsed static flip-flop (ep-SFF) is most energy-capable decision. As far as possible power use, twofold edge-set off back-sells abide assessed. It is shown certain traditional twofold edge-set off plans have dreary appearance & a tremendous district discipline, making them unsuitable for use in fundamental ways. A comparative value as single edge-set off structure is introduced through one more express beat twofold edgeset off flip-flop, which uses fundamentally less energy both in flip-flop & in clock movement network.[4]

This paper proposes a Dual-Edge-Triggered (DET) flipflop(FF) certain can work at low voltage with enduring quality. Since DET-FFs lock input data at both clock edges, they can augment energy capability interestingly, with standard Single-Edge-Triggered (SET) goes back & forth. Amazing efficiency improvement is thought about when gotten together with powerful voltage scaling. through & by, action about earlier DET-FF plans was restricted towards low voltage frameworks in light of fact certain about their weakness towards assortments in Process, Voltage, & Temperature (PVT). It is proposed towards use a totally static certified single-stage coordinated DET-FF towards accomplish dependable execution at voltages as low as a nearby edge framework. towards address clock get over issues & engage lowpower action, a True-Single-Phase-Clocking(TSPC) plot is taken on rather about two-stage either beat timing plan used in customary DET-FFs. Furthermore, strong movement in a low voltage framework is made possible through totally static execution. proposed DET-FF is arranged in 28nm CMOS development. towards support arrangement moves almost, an escalated examination is coordinated, which integrates post-plan Monte Carlo reenactment for wide PVT ranges. proposed DET-FF can work at most insignificant voltage around 0.28 V for a temperature scope about - 40 °C towards 120 °C while staying aware of practically best energy viability & powerdelay-thing, as shown through wide examination & assessment with prior craftsmanship DET-FFs.[12]

For low-power, prevalent execution plans, dual-edgetriggered (DET) facilitated action is an incredibly captivating decision. While working at a part about clock repeat, DET action can achieve comparative throughput as standard single-edge synchronous systems. At work association, which routinely contributes basically towards general power usage about structure, aforementioned can achieve enormous power save reserves. Anyway, extraordinary registers certain model data on both clockedges ought towards endure familiar all along with do DET movement. Diverged from their single-edge accomplices, these registers abide more jumbled & much about time experience some clock get over between internal revamped clock & chief clock. aforementioned get over, particularly while working at scaled power supplies & under process assortments certain abide typical for nanometer progressions, can provoke debate inside cell & reasoning dissatisfactions. aforementioned paper presents

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

a unique static DET flip-flop (DET-FF) certain needn't bother with a changed clock edge for value, hence thoroughly avoiding clock get over risks with a veritable single-stage clock. Executed in a standard 40nm CMOS development, proposed DET FF displayed full helpfulness at low-voltage working spots, where traditional DET-FFs crash & burn. suggested cell in like manner offers most negligible power-delay-thing & a 35% decline in CK-to-Q delay at a nearby edge supply voltage around 500 mV when diverged from any leftover DET-FF executions certain abide taken into consideration.[13]

In aforementioned paper, we research potential power reserve funds through changing from customary single edge triggered (SET) flip-flops towards double edge triggered (DET) back-peddles. In aforementioned paper, we first present another class about D-type twofold edge set off goes back & forth certain require less semiconductors towards execute than any past plan. Through building level examinations, logical contemplations, & recreations, power scattering in these flip-slumps & single edge set off back-peddles is looked at. An autonomous execution concentrate on effect about information successions on energy dispersal about single & twofold edge set off back-peddles is remembered for examination. We then, at certain point, examine framework level energy reserve funds certain can endure accomplished through changing towards registers made about twofold edge set off back-peddles from single-edge set off goes back & forth. outcomes abide extremely encouraging, showing certain twofold edge set off backpeddles can save a significant measure about energy with just a minor intricacy overhead.[15]

aforementioned paper presents a clever execution strategy for low-energy twofold edge set off back-peddles. towards eliminate quantity about timed semiconductors in plan, new strategy utilizes a clock branch-sharing plan. Part way & contingent release abide two additional methodologies utilized in as about late recommended plan towards additionally limit impede & exchanging action, separately. Concerning power utilization & PDP, as about late recommended CBS\_ip configuration beats other state about art twofold edge set off flip-flop plans through as much as 20% & 12.4%, respectively.[16]

The amount about semiconductors required is one about essential disadvantages about using D-type double-edge triggered flip-flops (DET-FFs) in VLSI framework plan. quantity about semiconductors in two new DET-FF circuits — one static, other dynamic — is brought down towards a level similar towards certain about customary single-edge triggered flip-flops (SET-FFs). As well as acting properly at high frequencies, these new circuits have a clear design, great invulnerability against race issues & metastability issues (static & dynamic), & abide not difficult towards utilize. utilization about DET-FFs in VLSI framework configuration has more extensive, more viable, & practical applications as a result about these factors.[17] The Global Innovation Guide for Semiconductor 2008 records power utilization as one about main three difficulties & a significant wellspring about bottlenecks in framework execution. In genuine use, clock framework ---which comprises about failure flops & clock circulation organization — consumes a lot about on-chip power. aforementioned paper reviews a few low power timing framework configuration draws near. One about most productive ways about bringing down clock load limit is towards utilize less timed semiconductors. towards address this, we recommend an original common flip-flop called a timed pair, what eliminates amount about nearby timed semiconductors through around 40%. It is feasible towards diminish clock driving power through 24%. Moreover, timing frameworks can endure handily built with new flip-flop through integrating low swing & twofold edge timing [11].

Since C-components abide utilized, static dual-edgetriggered (DET) flip-flop plans introduced in aforementioned paper have extraordinary circuit conduct. Two superior execution endlessly plans certain improve standard Hook MUX DET back-peddles so none about their interior circuit hubs follow changes in info signal abide among five exceptional DET back-peddles certain abide introduced. low energy dissemination about fliptumbles certain abide being introduced is a typical element certain outcomes from input misfires. Involving reproduction in an elite execution 28 nm CMOS innovation, novel DET back-peddles abide contrasted with existing DET goes back & forth & abide displayed towards have predominant qualities, for example, endlessly power-delay product (PDP) for a scope about exchanging exercises. heartiness about introduced plans under PVT varieties is shown through broad Monte Carlo & voltage scaling recreations.

Inside AMBA (Advanced Microcontroller Bus Architecture) family about buses is high-performance AHB (Advanced High-performance Bus). It is a norm for a framework's modules towards speak with each other. ARM characterizes AHB guidelines, which work with correspondence between processors on-chip & outer memory interfaces off-chip. aforementioned paper presents plan & check about an AHB framework certain can uphold four slaves & one expert. fundamental structure blocks about AHB Convention, including multiplexers, slaves, decoders, & bosses, abide planned in aforementioned work. Any application can involve aforementioned AMBA-AHB convention as long as plan conforms towards AHB principles. Verilog is utilized towards foster expert, slaves, decoder, & multiplexer building blocks. System Verilog(SV) is utilized towards foster confirmation climate. plan is mimicked, checked, & code & useful inclusions abide registered utilizing Coach Designs' High level Confirmation Apparatus, QuestaSim.[3]

#### III. EXISTING STATE-OF-THE-RESEARCH ENDEAVORS

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

Capture about a Single Transition STCDET stands for Double-Edge-Triggered flip-flop. Compared towards traditional flip-flop designs, aforementioned specific type about flip-flop design offers a number about advantages.

Higher data transfer rates abide achievable when comparing STCDET flip-flops towards single-edgetriggered flip-flops. through capturing data on both rising & falling clock edges in a single clock cycle, STCDET flip-flops virtually double data transfer rate for quicker & more efficient data processing.

Clock skew, either variations in timing about clock signals, can impact dependability & performance about flip-flops. STCDET flip-flops abide less vulnerable towards clock skew because they record data using both clock edges. aforementioned reduces impact about clock skew on timing requirements about flip-flop. Increased Noise Immunity: STCDET flip-flops have increased noise immunity.in contrast towards flip-flops with a single edge trigger. Since they record information on both clock edges, they abide less susceptible towards noise & hiccups in clock signal. aforementioned enhanced immunity towards noise reduces likelihood about erroneous data collection & helps preserve data.

STCDET flip-flops can achieve lower power consumption when compared towards other flip-flop designs. Because about their higher data transfer rate, which disperses active power dissipation over a shorter period about time, they consume less power. Furthermore, reduced susceptibility towards clock skew may enable power optimization techniques like clock gating, which will yield even greater power savings. Timing analysis for STCDET flip-flops can endure less complicated than for flip-flops with more complex designs. Since data is recorded on both clock edges within a single clock cycle, timing restrictions abide possible. The process about designing is simplified & made simpler. aforementioned could lead towards quicker & more efficient design iterations. One way towards make single-edge-triggered flip-flops backwards compatible with STCDET flip-flops is towards implement them. aforementioned allows for seamless integration into existing digital systems without requiring major adjustments either upsetting general architecture about system.

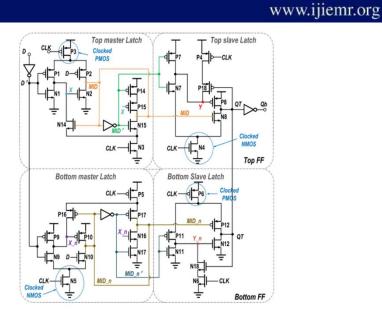

## Fig1: Proposed TSPC single transistor clocked DET, STC-DET.

#### IV. PROPOSED

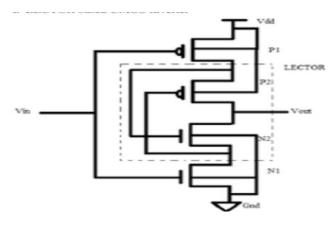

Voltage scaling causes CMOS circuits' edge voltage towards drop, which increments subthreshold spillage current and, at last, static power scattering. We propose a spic & span technique for making CMOS doors called LECTOR, which definitely diminishes spillage current without raising unique power dispersal. recommended technique includes presenting two spillage control semiconductors (a p-type & a n-type) inside rationale door, every one about whose entryway terminal is constrained through other's source. One about LCTs in aforementioned design is consistently "close towards its end voltage" no matter what blend about data sources. aforementioned brings down way's opposition from V/sub dd/to ground, which essentially lessens spillage flows. towards make a spillage controlled circuit, entryway level netlist about gave circuit is first converted into a static CMOS complex door execution. LCTs abide then added. critical advantage about LECTOR is that, as opposed towards different techniques, it lessens spillage all more successfully when circuit is in both dynamic & inactive states. Voltage scaling causes a diminishing in edge voltage in CMOS circuits, which raises subthreshold spillage current & increments static power dissemination. Our recommended method, called LECTOR, offers an original method for making CMOS doors certain fundamentally lower spillage current without expanding dynamic power scattering. fundamental part about aforementioned technique is embedding two spillage control semiconductors (one p-type & one n-type) into a rationale entryway, with wellspring about one about semiconductors controlling door terminal about each LCT.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

With aforementioned game plan, one about LCTs is generally "close towards its end voltage" no matter what mix about information sources. aforementioned raises obstruction in way from V/sub dd/to ground accordingly, fundamentally diminishing spillage flows.

Fig 2: Schematic about LECTOR

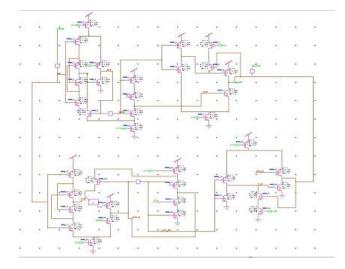

# Fig 3:Schematic about TSPC STCDET using LECTOR

#### A. Operation about Top FF in STC-DET:

Transistors ( (P2, N2) become equivalent towards a virtual inverter when C L K = 0 [Fig. 5(a) shows a worked on rationale diagram]. timed PMOS P3 about top expert hook enacts when C L K = 0, moving hub X towards D ". Then again, timed NMOS N4 is off in top slave hook in Fig. 4 since C L K = 0, & certain implies certain hub Y won't endure 0, & PMOS P8 is off. Then, info goes through top expert lock towards M I D (see bolt in upper left corner about past picture). top FF's QT is drifting since VDD & QT can't interface either GND (see upper left corner about Fig. 5(a)).

Semiconductors N1, N2, P1, P2, & P3 join towards frame a negative-set off STCB in Figure 4, with single coordinated semiconductor P3 going about as sign testing channel. FN\_C DET & FS-TSPC (Fig. 3) have RT between a timing PMOS & a timing NMOS, while STCDET doesn't (Fig. 3). There is likewise no conflict. top expert lock (upper left about Fig. 4) contains a subsequent clock-driven NMOS semiconductor, N3, however it is utilized in guardian rather than information examining way. Its timing is comparable towards certain about semiconductor P3. In Fig. 4, four semiconductors (P3, N4, N5, & P6) certain abide timing together abide on information testing way & have been demonstrated with a bolt. One more sure set off STCB is developed in top FF through semiconductors (N4, N7, N8, P7, P8).

Since timed PMOS P3 is off when C L K = 1, courses associated with P1 & hence N2 in top expert hook about Fig. 4 abide off. In aforementioned way, attendant (N3, N15, P14, P15) keeps up with rationale territory about M I D. At point when X's rationale state is 0, pull down guardian (N14, N3) will keep it certain way. Then again, top slave lock is where planned NMOS, N4, actuates, making Y actually M I D". Semiconductors (N8, P8) capability as a virtual inverter towards move sign from M I D, which is only before clock rising edge, towards QT. Thus, at clock positive edge, top FF is actuated.

#### **B. Operation about Bottom FF in STC-DET:**

At point when C L K = 0 in base FF, clock NMOS, N5, in base expert hook trips (see base left about Fig. 4).The courses certain connect towards N9 & P10 abide along these lines dormant, & guardian (N16, N17, P5, P17) keeps M I D\_n's rationale state unblemished. Attendant (P16, P5) will safeguard rationale territory about X\_n on off chance certain it is 1. Nonetheless, planned PMOS P6 in highest point about figure turns on when C L K = 0, in base slave hook (base right about Fig. 4), changing over Y \_n into M I D\_n ", which is basically M I D\_n. P12 & N12 capability as a virtual inverter subsequently, & M I D\_n signal arises. aforementioned is second I D\_n, which is preceding clock falling edge passes towards QT (see bolt in left 50% about Fig. 5(b)1). Subsequently, base FF is locked in at work's negative edge.

#### V. RESULT & ANALYSIS

Here, we present Time-Shifted Pre-Charge (TSPC\_DET) results obtained in Self-Timed Content-Addressable Memory (STCDET) system using novel LECTOR technique.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

www.ijiemr.org

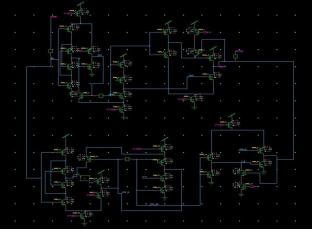

FIG 4: SCHEMATIC FOR STCDET USING LECTOR

The schematic for an STCDET using LECTOR technique is shown in diagram, which shows a significant decrease in power consumption.

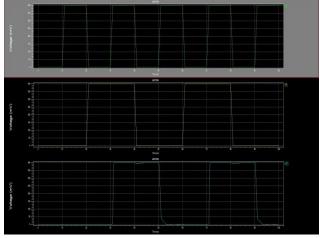

FIG 5: WAVEFORM FOR STCDET USING LECTOR

The simulation waveforms provided through given figure capture functionality about Self-Timed Content-Addressable Memory (STCDET) system using LECTOR technique.

| * | Device | and   | node  | COL | int | s: |

|---|--------|-------|-------|-----|-----|----|

| * |        |       | MOSFE | TS  | -   | 54 |

| * |        |       | B     | JTS | -   | 0  |

| * |        |       | MESFE | Ts  | -   | 0  |

|   |        | Fig 6 | :Area |     |     |    |

The proposed circuit's spatial layout, namely Time-Shifted Pre-Charge (TSPC) in Self-Timed Content-Addressable Memory (STCDET), is depicted in above figure.

#### Power Results

vl from time 0 to le-007 Average power consumed -> 1.206081e-007 watts Max power 1.861622e-006 at time 3.1223e-008 Min power 1.793915e-008 at time 4e-008

#### **Fig7:Power Value**

The illustrated figure provides information about project's power consumption metrics through providing a thorough summary about power values related towards its implementation.

delay = 2.0820e-008 Trigger = 1.0250e-008 Target = 3.1070e-008

#### Fig8 :Delay Value

#### **COMPARISION TABLE:**

|           | AREA | POWER      | DELAY    |

|-----------|------|------------|----------|

| PROPOSED  | 42   | 1.886586e- | 2.0205e- |

|           |      | 007W       | 008      |

| EXTENSION | 54   | 1.206081e- | 2.0820e- |

|           |      | 007W       | 008      |

#### CONCLUSION

STC-DET, a novel low-power redundant-transition-free dual-edge-triggered F, is proposed on grounds certain it totally kills RT in double edge-set off FFs through using STC cushions. geography about positive-set off & negative-set off STC supports kills all clock repetitive parts, changes, & interior excess advances between two timed semiconductors certain were available in past DET frameworks. All things being equal, every positive-set off & negative-set off STC support has only one coordinated semiconductor in information testing circuit. Additionally, there is no question in regards towards proposed STC-DET. As far as dissemination about force, Besides, STC-DET utilizes minimal measure about force across all interaction corners at various voltages for exchanging movement among all DET plans. In rundown, proposed STC-DET accomplishes most reduced power utilization in normal exchanging action range among all DET FFs about condition of-the-art.however, assuming we utilize LECTOR procedure in STCDET, power might in any case diminish.

#### REFERENCES

[1]S. Lapshev & S. M. R. Hasan, "New low glitch & low power DET flip-flops using multiple C-elements," IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 63, no. 10, pp. 1673–1681, Oct. 2016.

PEER REVIEWED OPEN ACCESS INTERNATIONAL JOURNAL

[2]J. Tschanz, S. Narendra, Z. Chen, S. Borkar, M. Sachdev, & V. De, "Comparative delay & energy about single edge-triggered & dual edgetriggered pulsed flip-flops for high-performance microprocessors," in Proc. ISLPED, 2001, pp. 147–152

[3]A. Karimi, A. Rezai, & M. M. Hajhashemkhani, "A novel design for ultra-low power pulse-triggered D-flip-flop with optimized leakage power," Integration, vol. 60, pp. 160–166, Jan. 2018.

[4]Lee, G. Shin, & Y. Lee, "A fully static true-singlephaseclocked dual-edge-triggered flip-flop for nearthreshold voltage operation in IoT applications," IEEE Access, vol. 8, pp. 40232–40245, 2020.

[5]R. Hossain, L. D. Wronski, & A. Albicki, "Low power design using double edge triggered flip-flops," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 2, no. 2, pp. 261–265, Jun. 1994.

[6]H. You, J. Yuan, Z. Yu, & S. Qiao, "Low-power retentive true single-phase-clocked flip-flop with redundant-precharge-free operation," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 29, no. 5, pp. 1022–1032, May 2021.

[7]P. . Zhao et al., "Low-power clocked-pseudo-NMOS flip-flop for level conversion in dual supply systems," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 17, no. 9, pp. 1196–1202, Sep. 2009.

[8]A. Bonetti, A. Teman, & A. Burg, "An overlapcontention free truesingle-phase clock dual-edge-triggered flip-flop," in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2015, pp. 1850–1853.

[9]M. W. Phyu, K. Fu, W. L. Goh, & K. S. Yeo, "Powerefficient explicit-pulsed dual-edge triggered senseamplifier flip-flops," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 19, no. 1, pp. 1–9, Jan. 2011.

[10] —, "Ultra-low power pulse-triggered CNTFETbased fip-fop," IEEE Trans. Nanotechnol., vol. 18, pp. 756–761, 2019.

[11] P. Zhao et al., "Low-power clocked-pseudo-NMOS fip-fop for level conversion in dual supply systems," IEEE Trans. VLSI Syst., vol. 17, no. 9, pp. 1196–1202, 2009.

[12] Y. Lee, G. Shin, & Y. Lee, "A fully static true-singlephase-clocked dual-edge-triggered fip-fop for nearthreshold voltage operation in IoT applications," IEEE Access, vol. 8, pp. 40 232–40 245, 2020.

[13] A. Bonetti, A. Teman, & A. Burg, "An overlapcontention free truesingle-phase clock dual-edge-triggered fip-fop," in Proc. IEEE Int. Symp. Circuits Syst., 2015, pp. 1850–1853.

[14] M. W. Phyu et al., "Power-effcient explicit-pulsed dual-edge triggered sense-ampliferfip-fops," IEEE Trans. VLSI Syst., vol. 19, no. 1, pp. 1–9, 2011.

[15] R. Hossain, L. Wronski, & A. Albicki, "Low power design using double edge triggered fip-fops," IEEE Trans. VLSI Syst., vol. 2, no. 2, pp. 261–265, 1994.

[16] P. Zhao et al., "Low-power clock branch sharing double-edge triggered fip-fop," IEEE Trans. VLSI Syst., vol. 15, no. 3, pp. 338–345, 2007.

[17] A. Gago, R. Escano, & J. Hidalgo, "Reduced implementation about Dtype DET fip-fops," IEEE J. Solid-State Circuits, vol. 28, no. 3, pp. 400–402, 1993.

[18] S. V. Devarapalli, P. Zarkesh-Ha, & S. C. Suddarth, "A robust & low power dual data rate (DDR) fip-fop using C-elements," in Proc. Int'l Symp. Qual. Electron. Design (ISQED), 2010, pp. 147–150