A Peer Revieved Open Access International Journal

www.ijiemr.org

### COPY RIGHT

2022 IJIEMR. Personal use of this material is permitted. Permission from IJIEMR must

be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 30th Jul 2022. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-11&issue= Spl Issue 06

## DOI: 10.48047/IJIEMR/V11/SPL ISSUE 06/31

Title LOW POWER AREA EFFICIENT ALU WITH LOW POWER FULL ADDER

Volume 11, SPL ISSUE 06, Pages: 167-170

Paper Authors

Dr.Nookala Venu, Ankitha Engli, Mrs Sandhya rani, Mithin Kumar Ananthula

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

# LOW POWER AREA EFFICIENT ALU WITH LOW POWER FULL ADDER

Dr.Nookala Venu

Professor Dept. of ECE Balaji Institute of Technology & Science Narsampet, Warangal, India

venunookala@gmail.com

Ankitha Engli UG Student Dept. of ECE Balaji Institute of Technology & Science Narsampet, Warangal, India adeputejaswini@gmail.com Mrs.Sandhya Rani Assistant Professor Dept. of ECE Balaji Institute of Technology & Science Narsampet, Warangal, India

sandhya597952@gmail.com

### Mithin Kumar Ananthula

UG Student Dept. of ECE Balaji Institute of Technology & Science Narsampet, Warangal, India

billa.shashank123@gmail.com

*Abstract*— In this paper implemented a low Power Area efficient ALU using XNOR logic. The 4bit ALU design. ALU is an Arithmetic and Logic Unit, which performs arithmetic operation like ADD, SUB, PASS THROUGH, TWO'S COMPLEMENT, etc. and logic operation like AND, OR, EXCLUSIVE OR, EXCLUSIVE NOR, etc. Full adder is the basic component for an ALU. By reducing the power of full adder, the ALU power also be reduced. Compared with Gate Diffusion Input Full Adder, 50% power reduced in the XNOR based Full Adder Technique. The simulation is carried out using Microwind DSCH3.

### I. INTRODUCTION

In the era of growing technology and scaling of devices up to nanometer regime, the arithmetic logic circuits are to be designed with compact size, less power and propagation delay. Arithmetic operations are indispensable and basic functions for any high speed low power application digital signal processing, microprocessors, image processing etc. Addition is most important part of the arithmetic unit rather approximately all other arithmetic operation includes addition<sup>[7]</sup>. Thus, the primary issue in the design of any arithmetic logic unit is to have low power high performance adder cell. Power has become one of the major important issues in the VLSI circuits. As the complexity increases and number of transistors in a chip increase, one has to consider the power dissipation. Higher power dissipation, increases the temperature and hence increases the chip temperature. As power dissipation goes on increasing, the battery life, reliability, cooling system and cost are affected [8]. Hence as a designer it is important to design circuits to consume less power by avoiding unwanted switching actions [9].

The majority of the power dissipation is due to dynamic power dissipation. That is due to switching action of the node and internal node capacitance of the circuit [10]. Other sources of power dissipation are static current and short circuit current. Static power dissipation is basically due to the reverse current and sub threshold current when the transistor is off [11]. Compared to dynamic power dissipation, static power is less around (20% - 50%) but increases as complexity increases. Short circuit current is due to non-zero rise time and fall time and is around (5% - 10%). Many techniques are used to reduce the leakage current and hence to reduce the static power dissipation such as power gating, multiple Vt, etc. There are many techniques involved to reduce the dynamic power dissipation by reducing the switching action such as Block enabling, Pre computation technique, etc... Clock gating technique is used to reduce the clock power. The dynamic power dissipation is around (40%-70%) and is relatively reducing with today's technology. An Arithmetic and Logic Unit (ALU) is a digital circuit that performs arithmetic and logic operations. The ALU is a fundamental building block of the central processing unit of a computer [12]. The power consumed by the ALU has a direct impact in the power dissipated from the processor. Hence, a design is required to implement the ALU in a fashion where the performance of the processor is improved and also the power consumed is less [13]. To be precise Power consumption of whole data path can be reduced by reducing power consumption of ALU. Adder is the basic building block for an ALU. To reduce the power consumption from ALU first we need to reduce through full adder. ALU (Arithmetic Logic Unit)

The heart of every computer is an Arithmetic Logic Unit (ALU). This is the part of the computer which performs

A Peer Revieved Open Access International Journal

www.ijiemr.org

arithmetic operations on numbers, e.g. addition, subtraction, etc. In this lab you will use the Verilog language to implement an ALU having 10 functions. Use of the case structure will make this job easy[14]. The ALU Design and Operation A 4 - bit ALU has been designed for 3.0 V operation in which, the full adder design has been implemented using MIFG CMOS inverters. The ALU has four stages, each stage consisting of three parts: a) input multiplexers b) full adder and c) output multiplexers. The ALU performs the following four arithmetic operations, ADD, and SUBTRACT INCREMENT and DECREMENT. The four logical operations performed are EXOR, EXNOR, AND and OR. The input and output sections consist of 4 to 1 and 2 to 1 multiplexers. The multiplexers were designed using the pass transistor logic. A set of three select signals has been incorporated in the design to determine the operation being performed the inputs and outputs being selected [15].

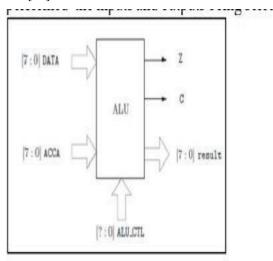

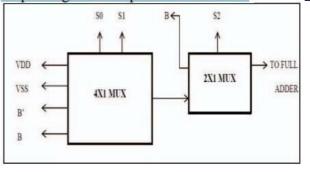

Fig 1: ALU Block Diagram

### DESIGN OF ALU USING LOW POWER FULL ADDER

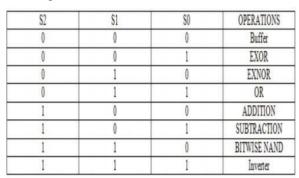

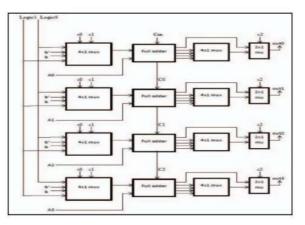

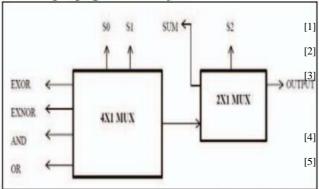

An arithmetic and logic unit is a fundamental block for many processors. It performs many processors [16]. It performs many operations like addition, subtraction, XOR, XNOR, buffer, NAND, OR etc. The 4 bit ALU operation can be implemented using eight 4x1 multiplexer, four full adder, four 2x1 multiplexer [17]. Depends upon the three selection line s2, s1, s0, the arithmetic and logic operation can be performed. The block of 4x1 multiplexer consists of four inputs, which is logic 0, logic 1, B and B'. Depends upon the s0 and s1 selection line; the desired output can be generated. These outputs [18]. The next stage of 4x1 multiplexer has the input of full adder sum, which is EXOR, EXNOR, AND, and OR. Depends on the s0 and s1 selection lines, the output can be generated. It acts as an input for the 2x1 multiplexer. Another input of 2x1 multiplexer is the full adder sum output. Finally, the output stage of 2x1 multiplexer can be generated by using s2 selection line.

#### Table: Operations of ALU

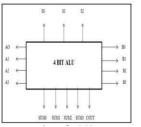

Fig.2: Logo representation of ALU

Fig 3: Process of 4bit arithmetic and logic unit

Multiplexer logic at the input stage consists of 4x1 multiplexer and 2x1 multiplexer. Depends upon the selection line of s0, s1 and s2, the output of full adder has been computed. Multiplexer logic at the output stage consists of 4x1 multiplexer and 2x1 multiplexer. Depends upon the selection line of s0, s1, and s2, the output of ALU has been computed. Input stage multiplexer consists of VDD, VSS, B and B'. The output stage multiplexer consists of EXOR, EXNOR, AND and OR input. Fig.8 shows input stage of multiplexer architecture and fig9 shows output stage of multiplexer architecture.

A Peer Revieved Open Access International Journal

### www.ijiemr.org

Fig 4: Architecture of multiplexer logic at the input stage

This paper presents a new technique of XNOR logic, to design the full adder is resolved by gate diffusion input technique which proven to have high power consumption and compared with XNOR logic. These new approach of XNOR logic gives excellent result then previous design in charge of power consumption, area as well as propagation delay.

Fig.5: Architecture of multiplexer logic at the output stage

### LAYOUT DESIGN LAYOUT DESIGN FOR ALU

SIMULATION RESULTS

#### REFERENCE

- R. Shalem, E. John, and L.K.John, "A novel lowpower energyrecovery full adder cell," in Proc. Great Lakes Symp.VLSI,Feb. 1999, pp.380–383 .

- A.Sharma, R Singh and R. Mehra, "Low Power TG Full Adder Design Using CMOS Nano Technology,".

- L.Bisdounis, D.Gouvetas and O.Koufopavlou, "A comparativestudy of CMOS circuit design styles for lowpower high-speedVLSI circuits" Int. J. of Electronics, Vol.84, No.6, pp 599-613,1998. Anu Gupta, Design Explorations of VLSI ArithmeticCircuits, Ph.D. Thesis, BITS,Pilani, India, 2003.

- T. Esther Rani, M. Asha Rani, Dr.Rameshwarrao, "Areaoptimized Low Power Arithmetic And Logicunit".

- R.Zimmermannn and W.Fichtner, "Low power logic styles:CMOS versus pass-transistor logic," IEEE J. Solid-StateCircuits, vol. 32, pp. 1079–1090, July 1997. Y.Jiang, Y.Wang,and J.Wu, "Comprehensive Power Evaluation of Full Adders,"Florida Atlantic Univ., Boca Raton, Tech. Rep., 2000.

- [6]. R.Uma and P. Dhavachelvan," Modified Gate Diffusion InputTechnique: A New Technique for Enhancing Performance inFull Adder Circuits" 2nd International Conference on Communication, Computing & Security [ICCCS-2012].

[7] Karthik Kumar Vaigandla, Dr.N.Venu, " Survey on Massive MIMO: Technology, Challenges, Opportunities and Benefits," YMER, VOLUME 20 : ISSUE 11 (Nov) - 2021, Page No:271-282.

[8] Karthik Kumar Vaigandla and Dr.N.Venu, "A Survey on Future Generation Wireless Communications - 5G : Multiple Access Techniques, Physical Layer Security, Beamforming Approach", *Journal of Information and Computational Science*, Volume 11 Issue 9, 2021, pp.449-474.

[9] Karthik Kumar Vaigandla and Dr.N.Venu, "BER, SNR and PAPR Analysis of OFDMA and SC-FDMA," GIS SCIENCE JOURNAL, ISSN NO : 1869-9391, VOLUME 8, ISSUE 9, 2021, pp.970-977.

[10] Dr.Nookala Venu, Dr.A.ArunKumar and Karthik Kumar Vaigandla. Review of Internet of Things (IoT) for Future Generation Wireless Communications. International Journal for Modern Trends in Science and Technology 2022, 8(03), pp. 01-08.

[11] A. V. L. N. Sujith, R. Swathi, R. Venkatasubramanian, Nookala Venu, S. Hemalatha, Tony George, A. Hemlathadhevi, P. Madhu, Alagar Karthick, M. Muhibbullah, Sameh M. Osman, "Integrating Nanomaterial and High-Performance Fuzzy-Based Machine Learning Approach for Green Energy Conversion" Journal of Nanomaterials, ISSN: 1687-4129,Volume 2022,PP:1-11.

[12] Nookala Venu, D. Yuvaraj, J. Barnabas Paul Glady, Omkar Pattnaik, Gurpreet Singh, Mahesh Singh, and Amsalu Gosu Adigo, "Execution of Multitarget Node Selection Scheme for Target Position

A Peer Revieved Open Access International Journal

www.ijiemr.org

Alteration Monitoring in MANET", Wireless Communications and Mobile Computing, ISSN:1530-8669, Volume 2022, PP: 1-9.

[13] Nookala Venu, R.Swathi, Sanjaya Kumar Sarangi, V. Subashini, D. Arulkumar, Shimpy Ralhan, Baru Debtera, "Optimization of Hello Message Broadcasting Prediction Model for Stability Analysis", Wireless Communications and Mobile Computing, ISSN:1530- 8669, Volume 2022, PP: 1-9.

[14] Nookala Venu, Karthik Kumar Vaigandla, Dr.A.ArunKumar, "Investigations of Internet of Things (IoT): Technologies, Challenges and Applications in healthcare", International Journal of Research (IJR), ISSN: 2236-6124, Volume XI, Issue II, Feb 2022, PP: 143-153

[15] Dr. Nookala Venu, "Analysis of Xtrinsic Sense MEMS Sensors" International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering (IJAREEIE), ISSN:2278-8875 Vol 4, Issue:8, August 2015, PP: 7228-7234.

[16] Nookala Venu, Asiya Sulthana, "Local Mesh Patterns for Medical Image Segmentation" Asian Pacific Journal of Health Sciences (APJHS), e-ISSN: 2349-0659 p-ISSN: 2350-0964, Vol. 5, Issue 1, March 2018, PP: 123-127.

[17] Dr Nookala Venu, Mrs Asiya Sulthana "Local Maximum Edge Binary Patterns for Medical Image Segmentation, International Journal of Engineering and Techniques (IJET), ISSN: 2395-1303, Volume 4 Issue 1, Jan-Feb 2018, PP: 504-509.

[18] Dr.N.Venu, Dr.A.Arun Kumar, "Comparison of Traditional Method with watershed threshold segmentation Technique", International Journal of Analytical and Experimental Analysis (IJAEMA), ISSN: 0886-9367, Volume XIII, Issue 1, January- 2021, PP:181-187.

[19] Karne, RadhaKrishna, and T. K. Sreeja. "ROUTING PROTOCOLS IN VEHICULAR ADHOC NETWORKS (VANETs)." *International Journal of Early Childhood* 14.03: 2022.

[20] Karne, RadhaKrishna, et al. "Optimization of WSN using Honey Bee Algorithm."

[21] RadhaKrishna Karne, Dr TK. "COINV-Chances and Obstacles Interpretation to Carry new approaches in the VANET Communications." *Design Engineering* (2021): 10346-10361.

[22] Karne, RadhaKrishna, et al. "Simulation of ACO for Shortest Path Finding Using NS2." (2021): 12866-12873.

[23] RadhaKrishna Karne, Dr TK. "Review On Vanet Architecture And Applications." *Turkish Journal of Computer and Mathematics Education* (*TURCOMAT*) 12.4 (2021): 1745-1749.

[24] Karne, Radha Krishna, et al. "GENETIC ALGORITHM FOR WIRELESS SENSOR NETWORKS."