A Peer Revieved Open Access International Journal

www.ijiemr.org

### COPY RIGHT

**2017 IJIEMR**. Personal use of this material is permitted. Permission from IJIEMR must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works. No Reprint should be done to this paper, all copy right is authenticated to Paper Authors

IJIEMR Transactions, online available on 30<sup>th</sup> Nov 2017. Link

:http://www.ijiemr.org/downloads.php?vol=Volume-6&issue=ISSUE-11

Title: FFT COPROCESSOR BASED BSD REPRESENTATION FOR FLOATING-POINT BUTTERFLY ARCHITECTURE

Volume 06, Issue 11, Pages: 499–506. Paper Authors

### **M.ANUSHA**, G.NAGESHWAR RAO

Bomma Institute of Technology and Science

USE THIS BARCODE TO ACCESS YOUR ONLINE PAPER

To Secure Your Paper As Per UGC Guidelines We Are Providing A Electronic Bar Code

A Peer Revieved Open Access International Journal

www.ijiemr.org

### FFT COPROCESSOR BASED BSD REPRESENTATION FOR FLOATING-POINT BUTTERFLY ARCHITECTURE <sup>1</sup>M.ANUSHA, <sup>2</sup>G.NAGESHWAR RAO

<sup>1</sup>M.ANUSHA , <sup>2</sup>G.NAGESHWAR RAO <sup>1</sup>M.Tech Scholar,Dept OF ECE, Bomma Institute of Technology and Science <sup>2</sup> Assistant Professor,Dept of ECE, , Bomma Institute of Technology and Science

#### Abstract:

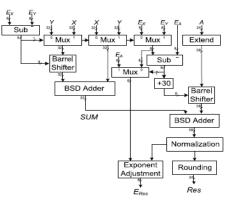

Fast Fourier transform (FFT) coprocessor, hosting a critical effect on the execution of correspondence systems, need been An high temp subject for research to a significant number a considerable length of time. Those FFT work comprises about successive increase include operations through unpredictable numbers, dubbed as butterfly units. Applying floating-point (FP) math on FFT architectures, particularly butterfly units, need ended up additional prevalent as of late. It offloads compute-intensive assignments from universally useful processors Eventually Tom's perusing dismissing FP worries (e.g. scaling and overflow/underflow). However, the major downside for FP butterfly is its gradualness in examination for its fixed-point partner. This uncovers the impetus to create A high-sounding FP butterfly building design will relieve FP gradualness. This short proposes A quick FP butterfly unit utilizing a concocted FP fused-dot-product-add (FDPA) unit, with figure Abdominal muscle  $\pm$  cd  $\pm$  E, dependent upon binary-signeddigit (BSD) representational. The FP three-operand BSD snake and the FP BSD steady multiplier need aid the constituents of the suggested FDPA unit. An carry-limited BSD snake will be suggested what's more utilized in the three-operand snake and the parallel BSD multiplier thereabouts Likewise will enhance those speed of the FDPA unit. Moreover, altered corner encoding may be used to quicken the BSD multiplier. The amalgamation Outcomes indicate that the recommended FP butterfly building design may be a significant part speedier over past counterparts However In those expense of All the more zone.

#### **1.INTRODUCTION:**

The complexity of communications and sign processing circuits increases each one year. This is made feasible with the aid of manner of the CMOS generation scaling that allows the combination of increasingly more transistors on a single tool. This progressed complexity makes the circuits extra liable to errors. On the identical time, the scaling manner that transistors carry out with lower voltages and are greater at risk of errors as a result of noise and production versions. Mild errors can trade the logical rate of a circuit node growing a brief error that may have an impact on the device operation. Another desire is to layout number one circuit blocks or entire layout libraries to decrease the possibility of mild mistakes. In the end, it's also viable to add redundancy at the

A Peer Revieved Open Access International Journal

www.ijiemr.org

system stage to detect and accurate mistakes One classical instance is using triple modular redundancy (TMR) that triples a block and votes a number of the three outputs to find out and correct errors. The precept difficulty with the ones smooth mistakes mitigation strategies is that they require a massive overhead in terms of circuit implementation. Every different approach is to attempt to use the algorithmic residences of the circuit to find/correct mistakes. This is commonly known as set of rules-primarily based totally fault tolerance (ABFT). This approach can lessen the overhead required to shield a circuit. Sign processing and communications circuits are nicely right for ABFT as they've got ordinary structures and plenty of algorithmic residences. Over the years, many ABFT techniques had been proposed to defend the number one blocks which are generally used in the ones circuits. Numerous works have considered the safety of virtual filters. The understanding of the distribution of the clear out output has additionally been these days exploited to discover and accurate errors with decrease overheads. The protection of speedy Fourier transforms (FFTs) has additionally been widely studied. As sign-processing circuits come to be extra complicated, it's far commonplace to locate several filters or FFTs operating in parallel. This occurs for instance in filter out banks or in multiple-input multiple-output (MIMO) communication structures. This

approach can be used for operations, in which the output of the sum of numerous inputs is the sum of the individual outputs. This is authentic for any linear operation as, for instance, the discrete Fourier transforms (DFT).

### PROPOSEDPROTECTIONSCHEM ES FORPARALLELFFTS Floating-Point butterfly building design In light of double Signed-Digit representational.

Quick Fourier change (FFT) meandering comprises for a few sequential multipliers and adders over intricate numbers; Subsequently an suitable amount representational must be picked wisely. The vast majority of the FFT architectures bring been utilizing fixedpoint arithmetic, until as of late that FFTs In light of floating-point (FP) operations develop. Those principle advantage about FP again fixed-point math may be the totally element extent it introduces; Yet at those liability from claiming higher cosset. Moreover, utilization of IEEE-754-2008 standard for FP math considers an FFT coprocessor in cooperation for general end goal processors. This offloads compute-intensive assignments from the processors Also prompts higher execution. Those principle detriment of the FP operations is their gradualness in examination with those fixed-point counterparts. An approach should accelerate those FP math may be with blend few operations clinched а alongside An absolute FP unit, and Subsequently save delay, area, and force

A Peer Revieved Open Access International Journal

www.ijiemr.org

utilization. Utilizing excess amount frameworks is in turn well-known method for overcoming FP slowness, the place there will be no word-wide convey proliferation inside the intermediate operations. A number system, defined by a radix *r* and a digit-set  $[\alpha, \beta]$ , is redundant iff $\beta - \alpha + 1 > r$ .

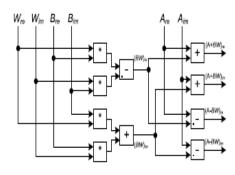

Fig.NFFT butterfly construction modeling with stretched intricate numbers.

Those conversion, from nonredundant, on a excess arrangement is a carry-free operation. This short proposes a butterfly building design utilizing excess FP arithmetic, which is of service for FP FFT coprocessors Also contributes on advanced indicator preparing provisions. 1) every last one of significands are quell clinched alongside double signeddigit (BSD) configuration and the relating carry-limited snake will be outlined. 2) configuration for FP steady multipliers to operands for BSD significands. 3) configuration about FP three-operand adders to operands with BSD significands. 4) plan from claiming FP fused-dot-product-add (FDPA) units (i. E., Abdominal muscle  $\bullet$  } cd  $\bullet$  } E) for operands for BSD significands.

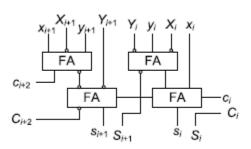

Fig. BSD adder (two-digit slice). TABLE GENERATION OF A PP

| $W_{i+1}^- W_{i+1}^+$ | $W_{i}^{-}W_{i}^{+}$ | $\ W_{i+1}^-W_{i+1}^+W_i^-W_i^+\ $ | PPi           |

|-----------------------|----------------------|------------------------------------|---------------|

| 0 0                   | 0 0                  | 0                                  | 0             |

| 0 0                   | 0 1                  | 1                                  | В             |

| 0 0                   | 1 1                  | -1                                 | -B            |

| 0 1                   | 0 0                  | 2                                  | $2 \times B$  |

| 1 1                   | 0 0                  | -2                                 | $-2 \times B$ |

# A. Suggested excess Floating-Point multiplier.

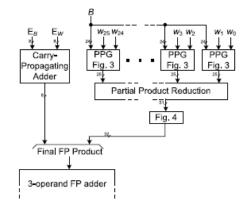

Those suggested multiplier, similarly different parallel multipliers, comprises from claiming two major steps, namely, halfway item era (PPG) Also PP diminishment (PPR). However, opposite of the traditional. Multipliers, our multiplier keeps those result clinched alongside excess arrangement and Subsequently there is no requirement for the last carry-propagating snake.

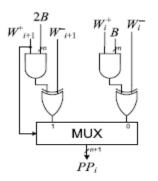

Partial Product Generation:

Partial Product Reduction:

Fig. Generation of the *i*th PP.

A Peer Revieved Open Access International Journal

www.ijiemr.org

32 digits to 3-operand adder

Fig. Digits to three-operand adder.

### Fig. Proposed redundant FP multiplier.

# **B.** Suggested excess Floating-Point Three-Operand snake.

The direct methodology with perform a three-operand FP expansion will be should link two FP adders which prompts.

## Fig. Suggested three-operand arrangement plan.

Helterskelter latency, power, Furthermore range utilization. A finer lifestyle may be to utilize combined three-operand FP adders [6], [7]. In the recommended three-operand FP adder, another arrangement piece will be executed Also CSA–CPA need aid traded Toward those BSD adders. Moreover, sign rationale is wiped out.

# Fig.Recommended FP three-operand expansion.

Combined Eventually Tom's perusing different FP operations, includes a additional cycle of the entirety FFT unit.

### ADVANTAGES OF VLSI:

• Size: incorporated circuits need aid a great part smaller—both transistors

• **Speed**: signs could make switched the middle of rationale 0 and rationale 1 a great part snappier inside a chip over they could the middle of chips

• **control consumption:** rationale operations inside a chip likewise detract considerably lesquerella energy.

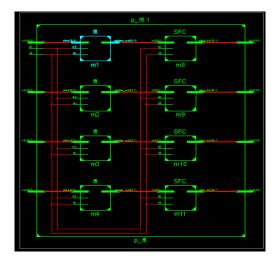

### RTL SCH

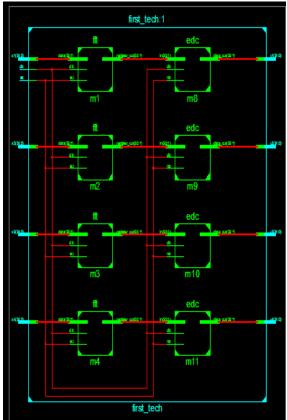

Fig 7.1:RtlSch of Parallel fft

A Peer Revieved Open Access International Journal

www.ijiemr.org

| Device Utilization Summary (estimated values) |      |     |           |             | Ð   |

|-----------------------------------------------|------|-----|-----------|-------------|-----|

| Logic Utilization                             | Used |     | Available | Utilization |     |

| Number of Slice Registers                     |      | 228 | 69120     |             | 0%  |

| Number of Sice LUTs                           |      | 292 | 69120     |             | 0%  |

| Number of fully used LUT-FF pairs             |      | 104 | 416       |             | 25% |

| Number of bonded ICBs                         |      | 254 | 640       |             | 39% |

| Number of BUFG/BUFGCTRLs                      |      | 1   | 32        |             | 3%  |

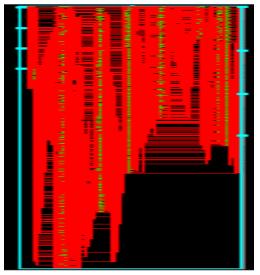

Table Estimated values of Parallel fft 7.1.2 TECHNOLOGY SCH:-

Fig: technology Sch of Parallel fft

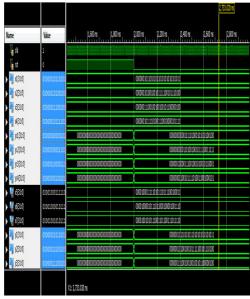

#### Simulation Results:-

#### Area:-

| Device Utilization Summary (estimated values) |      |           |             |  |

|-----------------------------------------------|------|-----------|-------------|--|

| Logic Utilization                             | Used | Available | Utilization |  |

| Number of Slice Registers                     | 228  | 69120     | 0%          |  |

| Number of Slice LUTs                          | 292  | 69120     | 0%          |  |

| Number of fully used LUT-FF pairs             | 104  | 415       | 25%         |  |

| Number of bonded 108s                         | 254  | 640       | 39%         |  |

| Number of BUFG/BUFGCTRLs                      | 1    | 32        | 3%          |  |

Table :Estimated value of First Technique

#### Timing Summary:

Speed Grade: -1

Minimum period: 3.362ns (Maximum Frequency: 297.426MHz)

Minimum input arrival time before clock: 2.875ns

Maximum output required time after clock: 3.259ns

#### **RTL SCH:-**

Fig :Rtlsch for First Technique

A Peer Revieved Open Access International Journal

www.ijiemr.org

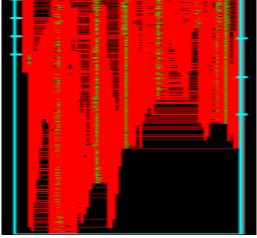

### **TECHNOLOGY SCH:-**

Fig: Technology of First Technique **Simulation Results:-**

|                                                    |                |          |        |                                         |              |                            |          |                        | 2, 193, 220 ns |     |

|----------------------------------------------------|----------------|----------|--------|-----------------------------------------|--------------|----------------------------|----------|------------------------|----------------|-----|

| Name                                               | Value          | ata a 18 | i00 ns | 1,700 ns                                | 1,800 ns     | 1,900 ns                   | 2,000 ns | 2,100 ns               | 2,200 ns       | 2,3 |

| la cik                                             | 1              |          |        |                                         |              |                            |          |                        |                |     |

| 🄓 ıst                                              | 0              |          |        |                                         | 1            |                            |          |                        |                |     |

| ▶ 🕌 x1β1x0)                                        | 01001001010000 |          |        |                                         | 0100100101   | 3000 100 10 100 10 100     | 10010    |                        |                |     |

| ▶ <table-of-contents> x2[31:0]</table-of-contents> | 00100010010010 |          |        |                                         | 0010001001   | 00 100 100 100 100 100 100 | 01000    |                        |                |     |

| 🕨 🕌 x8(61.0)                                       | 00100100100100 |          |        |                                         | 0010010010   | 01000100101111111          | 00010    |                        |                |     |

| ▶ <table-of-contents> x4[31x0]</table-of-contents> | 00100010001001 |          |        |                                         | 00 1000 1000 | 0010000100111100           | 10010    |                        |                |     |

| ▶ 🕌 y1[51:0]                                       | 00000010010011 |          | 0000   | 000000000000000000000000000000000000000 | 0000000000   |                            | 0000     | 00100100111000010      | 0 100 1000 10  |     |

| ▶ 🍟 y2[51x0]                                       | 00000011000100 |          | 0000   | 000000000000000                         | 00000000000  |                            | 0000     | 00110001001001001      | 0001000000     |     |

| ▶ 🕌 y3[31:0]                                       | 00800001001008 |          | 0000   | 000000000000000000000000000000000000000 | 0000000000   |                            | 0000     | 00010010000010001      | 0011111100     |     |

| ▶ 🕌 y4[51x0]                                       | 0000001000100  |          | 0000   | 000000000000000                         | 00000000000  |                            | 0000     | 00010001000100100100   | 0001110010     |     |

| ▶ 🐝 x[31:0]                                        | 10110010010008 |          |        |                                         | 1011001001   | 0000011001110100           | 01110    |                        |                |     |

| ▶ 👹 y11[B1:0]                                      | 01001001010000 |          | 0000   | 000000000000000                         | 0000000000   |                            | 0100     | 1001010000100101010    | 010 100 100 10 |     |

| 🕨 🙀 y22(31:0)                                      | 00100010010010 |          | 0000   | 000000000000000000000000000000000000000 | 0000000000   |                            | 0010     | 00 100 100 100 100 100 | 0010001000     | i   |

| ▶ 🕌 y33[31:0]                                      | 00100100100100 |          | 0000   | 000000000000000000000000000000000000000 | 00000000000  |                            | 0010     | 0 100 100 1000 100 101 | 1111100010     |     |

| 🕨 😽 y44[31:0]                                      | 00100010001001 |          | 0000   | 000000000000000000000000000000000000000 | 00000000000  |                            | 0010     | 00 1000 100 10000 100  | 1110010010     | į.  |

| ▶ 🙀 z[81:0]                                        | 10110010010000 |          | 0000   | 000000000000000000000000000000000000000 | 00000000000  |                            | 1011     | 00100100000011001      | 1010001110     | Ť.  |

## Fig:Simulation of First Technique Second Technique:-

Area:-

| Device Utilization Summary (estimated values) |      |           |             |  |

|-----------------------------------------------|------|-----------|-------------|--|

| Logic Utilization                             | Used | Available | Utilization |  |

| Number of Slice Registers                     | 228  | 69120     | 0%          |  |

| Number of Slice LUTs                          | 292  | 69120     | 0%          |  |

| Number of fully used LUT-FF pairs             | 104  | 416       | 25%         |  |

| Number of bonded IOBs                         | 254  | 640       | 39%         |  |

| Number of BUFG/BUFGCTRLs                      | 1    | 32        | 3%          |  |

Fig: Estimated values of Second Technique

### **Timing Summary**

Minimum period: 7.343ns (Maximum Frequency: 136.182MHz)Minimum input arrival time before clock: 5.092ns, Maximum output required time after clock: 4.040ns, Maximum combinational path delay: No path found

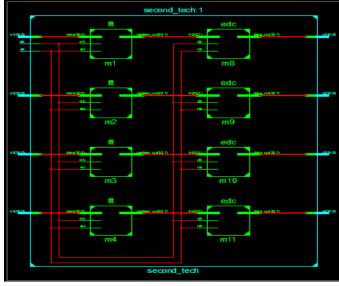

#### **RTL SCH:-**

Fig :Rtlsch of SecondTechnique

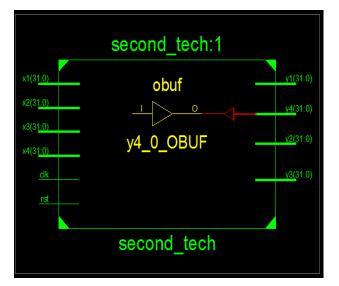

### **TECHNOLOGY SCH:-**

Fig:Technology of Second Technique

A Peer Revieved Open Access International Journal

www.ijiemr.org

| Simulation    | Results          |                                         |

|---------------|------------------|-----------------------------------------|

|               |                  |                                         |

| Name          | Value            | 1,400 ns 1,600 ns 1,800 ns              |

| l🔒 cik        | 0                |                                         |

| 埍 rst         | 0                |                                         |

| ▶ 📑 x1[31:0]  | 0001010101010101 |                                         |

| ▶ 📑 x2[31:0]  | 00010010100101   |                                         |

| ▶ 📑 x3[31:0]  | 00001001001001   |                                         |

| 🕨 📑 x4[31:0]  | 00010010001010   |                                         |

| 🕨 📲 y1[31:0]  | 00000010101010   | 000000000000000000000000000000000000000 |

| 🕨 📲 y2[31:0]  | 00000000100101   | 000000000000000000000000000000000000000 |

| 🕨 📲 уЗ[31:0]  | 0000001010010    | 000000000000000000000000000000000000000 |

| 🕨 📲 y4[31:0]  | 0000001100100    | 000000000000000000000000000000000000000 |

| 🕨 📲 x5[31:0]  | 00110001000011   |                                         |

| 🕨 👹 x6[31:0]  | 00111010000100   |                                         |

| 🕨 👹 x7[31:0]  | 00110000101000   |                                         |

| 🕨 📲 x[31:0]   | 01000011001110   |                                         |

| 🕨 💐 y11[31:0] | 0001010101010101 | 000000000000000000000000000000000000000 |

| 🕨 📲 y22[31:0] | 00010010100101   | 000000000000000000000000000000000000000 |

|               |                  | X1: 2,706.470 ns                        |

#### Simulation Results:-

Fig:Simulation of Second Technique **SYNTHESIS RESULTS**:

The formed one task may be mimicked Also checked their purpose. Once the utilitarian confirmation may be done, the RTL model may be made of the amalgamation methodology utilizing the Xilinx ISE device around. Over union process, the RTL model will make changed over of the entryway level netlist mapped with a particular innovation organization library. Here in this straightforward 3E family, Numerous distinctive gadgets were accessible in the Xilinx ISE device around. So as with union this configuration the gadget named as "XC3S500E" need been picked and the one bundle as "FG320" for those gadget velocity for example, such that "-4".

### **CONCLUSION:**

In this brief, those insurance of parallel FFTs execution against delicate errors need been contemplated. Two strategies bring been recommended and assessed. The recommended strategies are In light of joining together a existing ecc approach for those customary sorus weigh. Those sorus checks would used to identify Furthermore spot those errors Furthermore a straightforward equality FFT may be utilized for revision. The identification Furthermore area of the errors could a chance to be completed utilizing a sorus weigh for every FFT or on the other hand utilizing An situated about sorus checks that type a ecc. Those recommended systems have been assessed both As far as usage multifaceted nature Also lapse identification competencies. The Outcomes indicate that those second technique, which utilization equality FFT What's more a situated for sorus checks that manifestation a ECC, gives those best outcomes As far as usage As far as unpredictability. lapse protection, deficiency infusion trials show that the ecc plan could recoup every last one of errors that would crazy of the tolerance extent. Those flaw line scope for the parity-SOS plan and the parity-SOS-ECC plan is~99. 9% when the tolerance level for sorus check is 1.

#### REFERENCES

[1] N. Kanekawa, e. H. Ibe, t. Suga, What's more Y. Uematsu, reliability On electronic Systems: relief about fittings Failures, delicate Errors, and Electro-

A Peer Revieved Open Access International Journal

www.ijiemr.org

Magnetic Disturbances. New York, NY, USA: Springer-Verlag,2010.

[2] r. Baumann, "Soft errors in propelled PC systems," IEEE des. Test Comput., vol. 22, no. 3, pp. 258–266, May/Jun. Over 2,800 doctor look assignments led from April 1, 2009 to March 31, 2010.

[3] m. Nicolaidis, "Design to delicate lapse mitigation," IEEE Trans. Gadget mater. Rel., vol. 5, no. 3, pp. 405–418, sep. Over 2,800 doctor look assignments led from April 1, 2009 to March 31, 2010.

[4] a. L. N. Reddy What's more p. Banerjee, "Algorithm-based issue identification forsignal preparing applications," IEEE Trans. Comput. , vol. 39, no. 10, pp. 1304–1308, oct. 1990.

[5] t. Hitana Furthermore a. K. Deb, "Bridging simultaneous Also nonconcurrent slip identification for fir filters," over Proc. NorchipConf. ,nov. 2004, pp. 75–78.

[6] s. Pontarelli, g. C. Cardarilli, m. Re, What's more An. Salsano, "Totally issue tolerant RNS based fir filters," On Proc. Fourteenth IEEE Int. On-line test Symp. (IOLTS), Jul. 2008, pp. 192–194.

[7] b. Shim What's more n. R. Shanbhag, "Energy-efficient delicate error-tolerant advanced indicator processing," IEEE Trans. Exact vast scale Integr. (VLSI) Syst., vol. 14, no. 4, pp. 336–348, apr. 2006.

[8] e. P. Kim and n. R. Shanbhag, "Soft N-modular redundancy," IEEETrans. Comput., vol. 61, no. 3, pp. 323–336, deface. 2012.

[9] j. Y. Jou What's more j. An. Abraham, "Fault-tolerant FFT networks,"IEEE Trans. Comput., vol. 37, no. 5, pp. 548–561, might 1988. [10] What's more, the lion's share of Corps parts don't stay in their starting work areas once their comm. -J. Wang and n. K. Jha, "Algorithm-based deficiency tolerance for FFT networks,"IEEE Trans. Comput., vol. 43, no. 7, pp. 849-854, Jul. 1994.